SSD 基础概念

SSD 基本工作原理

SSD 硬件组成部分

SSD(Soild State Drive) 的硬件包括几大部分:主控、闪存、缓存芯片DRAM、PCB、接口。

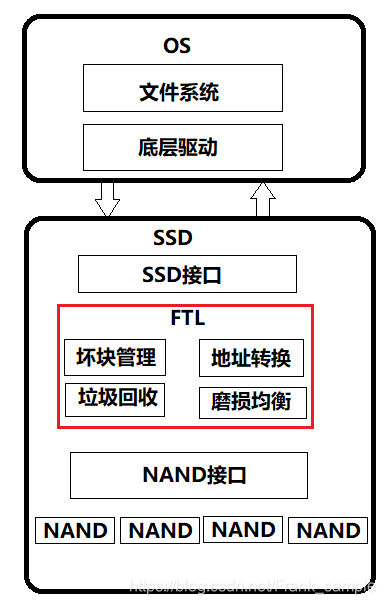

SSD 主要有三大功能模块组成

- 前端接口和相关的协议模块;

- 中间的FTL(Flash Translation Layer)模块;

- 后端和闪存通信模块;

SSD前端负责和主机直接通信,接受主机发送来的命令和数据,命令经SSD处理后(FTL模块),最终交由前端将命令状态或数据返回给主机。

SSD的写和读操作

主机通过接口发送写命令给SSD,SSD接收到命令后执行,并接受主机将要写入的数据。数据一般会先缓存在SSD内部的RAM中,FTL为每个逻辑数据块分配一个闪存地址,当数据凑到一定数量后,FTL(FTL主要完成逻辑数据到闪存空间的映射)发送写入闪存请求给后端,后端根据写请求,把缓存里的数据写到对应的NAND内存空间。

当主机发来读命令时,SSD能根据需要读取的逻辑数据块查找映射表(逻辑地址到物理地址转换的映射表),获取这些逻辑数据在闪存空间的位置,后端便能从闪存上把对应数据读到SSD内部缓存空间,然后前端负责把这些数据返回给主机。

SSD 指标

工作温度范围: 0~70℃,非工作温度范围:-50~90℃

性能指标:IOPS(读写性能)、吞吐量(顺序读写)、响应时间/延时

Endurance:(for example: 200GB SSD)

- 10 DWPD(Drive Writes Per Day)for 5 years

- TBW(Terabytes Written): 10 * 200 GB * 365 * 5 ≈ 3600 TB

数据可靠性:

- UBER:Uncorrectable Bit Error Rate,不可修复的错误比特率,在闪存应用中,指已经经过纠错码纠错,但仍无法纠正所有错误,与预期数据相较下的纠码失败率。

- RBER:Raw Bit Error Rate,原始的错误比特率,从闪存内读出,尚未经过纠错码纠错,与预期数据相较下的误码率。

- MTBF:Mean Time Between Failure,平均无故障工作时间,是衡量一个的可靠性指标。

功耗:Max active、Active、Idle、Standby、Sleep、DevSleep

最大功耗与发热控制:

SSD 最大功耗是 ASIC 主控 和 闪存模块。当SSD温度传感器侦测到温度达到阈值,如70℃时,固件会启动降温算法模块,限制闪存后端并发写的个数。当温度下降到阈值70℃以下后,SSD固件会重新恢复到正常的后端写并发个数。

SSD系统兼容性:

BIOS和OS的兼容性

(从测试角度)OS、CPU、BIOS、应用程序

- 电信号和硬件兼容性

容错处理

在主机端发生错误的条件下,SSD即使不能正常和主机交互数据,也至少要保证不变砖。

从设计角度考虑加入容错模块、加大系统兼容性测试的覆盖面,这些都是提高SSD系统兼容性的手段和方法。

BIOS 和 SSD 交互

SSD 上电加载后,主机 BIOS 开始自检,主机中的 BIOS 作为第一层软件和 SSD 进行交互的步骤如下:

- 和SSD发生连接,SATA 和 PCIe 走不同的底层链路连接,协商(negotiate)到正确的速度上,自此主机端和 SSD 连接成功;

- 发出识别 SSD 的命令(如 SATA Identify)来读取 SSD 的基本信息,基本信息包括产品型号(part number)、FW 版本号、产品版本号等,BIOS 会验证信息的格式和数据的正确性;

- 读取 SSD 的其他信息,如 SMART(Self-Monitoring, Analysis, and Reporting Technology),直到 BIOS 找到硬盘上的主引导记录 MBR(Master Boot Record),加载 MBR;

- MBR 开始读取硬盘分区表 DPT(Disk Partition Table),找到活动分区中的分区引导记录 PBR (Partition Boot Record),并且把控制权交给PBR;

- SSD 通过数据读写功能来完成 OS 加载。

SSD Driver 关键技术

- ID管理

- 纠错算法

- 逻辑物理映射

- 磨损平衡(wear-Leveling)

- 垃圾回收(Garbage Collection)

- 缓存策略

- 掉段保护(Sudden Power Off Recovery, SPOR)

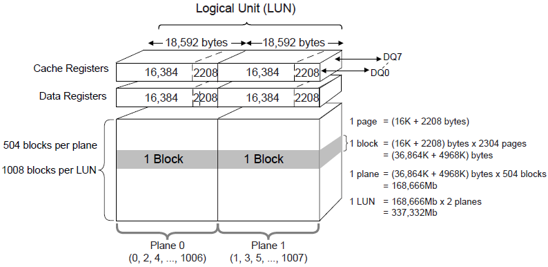

NAND 体系架构

Cache Registers: 供资料暂存或测试程式用,其读取跟写入速度都很快,断电后资料会遗失。

Data Registers: 用來暂存要放到page或从page取出的資料。

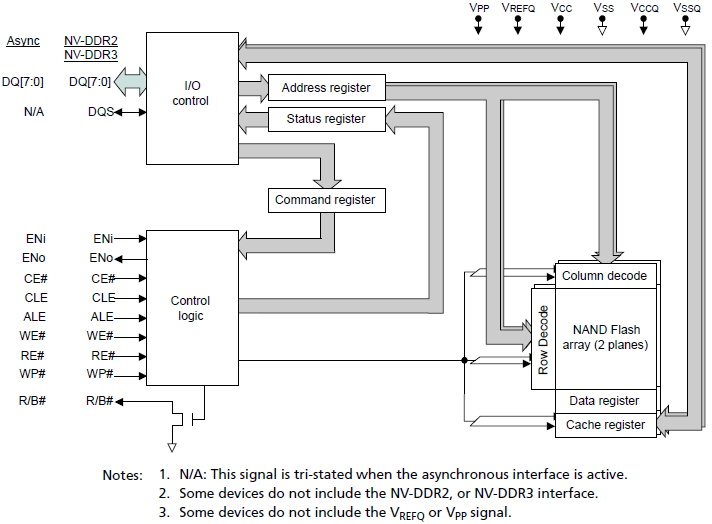

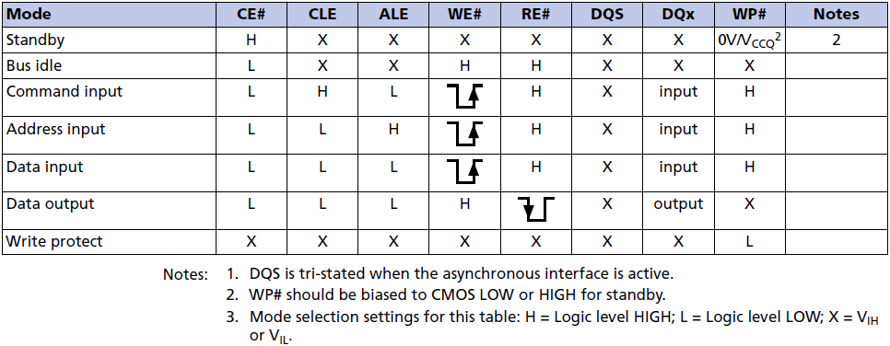

NAND 闪存接口(如 ALE/CLE):NAND 闪存的接口是并行总线(如 8 位 I/O),用于控制闪存芯片的操作(读/写/擦除)。

- ALE(Address Latch Enable):锁存地址信息。

- CLE(Command Latch Enable):锁存命令信息。

- 其他控制信号:WE#(写使能)、RE#(读使能)、CE#(片选)等。

- DQs: 数据选通,为数据输入/输出提供同步参考时钟

- DQs_t: 数据选通互补信号,NV-DDR2/DDR3接口中用于数据同步的互补参考信号

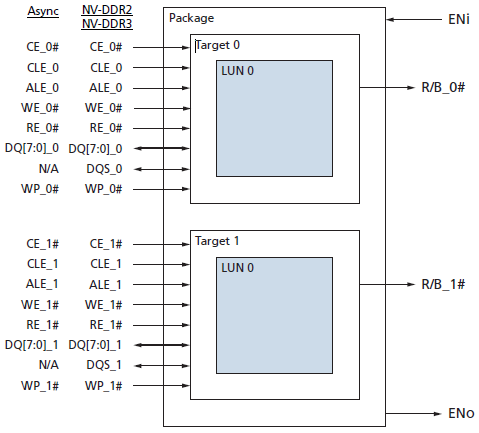

- ENi: 枚举输入,支持CE#引脚减少功能,菊花链中前一个NAND设备的ENo输出

- ENo: 枚举输出,连接至菊花链中下一个NAND设备的ENi引脚

- R/B#:就绪/忙,开漏输出(低电平有效),需外接上拉电阻,指示阵列活动状态

- VCC: 核心电源

- VCCQ: I/O电源

- VPP:可选高压电源,用于增强操作(如提升能效)

- VSS:核心地

- VSSQ:I/O地

- VREFQ:参考电压,用于NV-DDR2/DDR3接口

- ZQ:需通过RZQ电阻接地

- NC:无连接,内部未连接,可悬空或驱动

- DNU:请勿使用,必须悬空

- RFU:保留未来使用,必须悬空

数据线:通常为 8 位并行 I/O 总线(非差分信号),复用传输数据、地址和命令。

PCIe 是 SSD 与主机通信的高速串行接口,而 ALE/CLE 是 SSD 主控与 NAND 闪存芯片通信的并行控制信号。

LUN (Logical Unit Number,逻辑单元号)

在SSD中,LUN通常对应NAND闪存芯片的Die(晶圆)或Plane(平面),是主控管理闪存操作的最小逻辑单元。