#### **TLC 512Gb-8Tb NAND** B47R FortisFlash™ Features

# NAND Flash Memory - FortisFlash™

# MT29F512G08EBLEE, MT29F1T08EELEE, MT29F2T08EMLEE MT29F4T08EULEE, MT29F8T08EWLEE

#### B47R FortisFlash™ Features

- Open NAND Flash Interface (ONFI) 4.2-compliant<sup>1</sup>

- JEDEC NAND Flash Interoperability (JESD230D) compliant<sup>2</sup>

- Triple-level cell (TLC)

- Organization

- Page size x8: 18,352 bytes (16,384 + 1968 bytes)

- Block size: 2112 pages, (33,792K + 4059K bytes)

- Plane size: 4 planes x 556 blocks

- Device size: 512Gb: 2224 blocks; 1Tb: 4448 blocks; 2Tb: 8896 blocks; 4Tb: 17,792 blocks, 8Tb: 35,584 blocks

- NV-DDR3 I/O performance<sup>6</sup>

- Up to NV-DDR3 timing mode 15

- Clock rate: 1.25ns (NV-DDR3)

- Read/write throughput per pin: 1.6 GT/s

- TLC Array performance

- IWL READ operation time: 47us (TYP)

- READ PAGE operation time: 52us (TYP)

- Effective Program page time: 500us (TYP)

- Erase block time: 5ms (TYP)

- Operating Voltage Range

- V<sub>CC</sub>: 2.35-3.6V

- V<sub>CCO</sub>: 1.14-1.26V

- Command set: ONFI NAND Flash Protocol

- Data is required to be randomized by the external host prior to being inputted to the NAND device, see External Data Randomizaiton

- First block (block address 00h) is valid when shipped from factory. For minimum required ECC, see Error Management.<sup>5</sup>

- RESET (FFh) required as first command after pow-

- Operation status byte provides software method for detecting

- Operation completion

- Pass/fail condition

- Write-protect status

- Copyback operations supported within the plane from which data is read

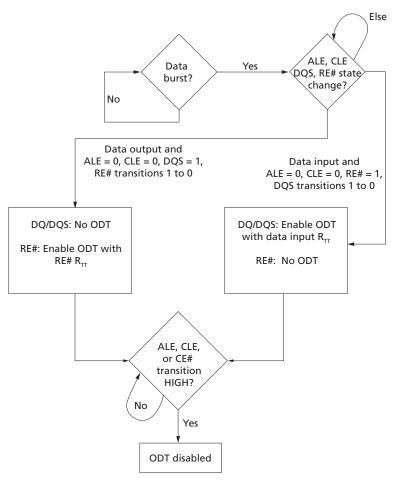

- On-die Termination (ODT)<sup>3</sup>

- Quality and reliability<sup>4</sup>

- Testing methodology: JESD47

- Data retention: See qualification report May vary for targeted application

- TLC Endurance: 3000 PROGRAM/ERASE cycles

- SLC Endurance: 60,000 PROGRAM/ERASE cycles

- This device is not intended for use in applications that require data to be pre-programmed in the NAND array prior to Reflow, Surface Mount, or any thermal processing. Please contact your Micron representative for details.

- Operating temperature:

- Commercial: 0°C to +70°C

- Package

- 132-ball BGA

- Notes: 1. The ONFI 4.2 specification is available at www.onfi.org.

- 2. The JEDEC specification is available at www.jedec.org/standards-documents.

- 3. ODT functionality is supported.

- 4. Read Retry operations and Auto Read Calibration operations are required to achieve specified endurance and for general array data integrity.

- 5. For minimum required ECC, see Error Management section.

- 6. The I/O performance quoted only applies to NAND packages and channel topologies with up to 4 die per channel load. The 16-die 2-channel package only supports up to 1200 MT/s. The maximum data rate the actual system can achieve however, depends heavily on the user's board design and topology. Thus, the user must determine whether their system can achieve the desired data rate through signal integrity simulations and analysis.

#### **TLC 512Gb-8Tb NAND B47R FortisFlash™ Features**

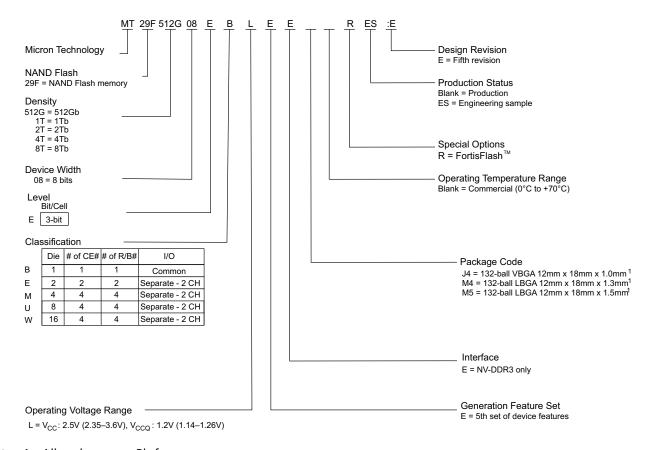

## **Part Numbering Information**

Micron NAND Flash devices are available in different configurations and densities. Verify valid part numbers by using Micron's part catalog search at www.micron.com. To compare features and specifications by device type, visit www.micron.com/products. Contact the factory for devices not found.

**Figure 1: Part Numbering Information**

Note: 1. All packages are Pb-free.

Figure 2: B47R Part Numbering Summary Table

| Device             | # of Die | Density | # of CE # | # of R/B # | I/O           | Package       | Thickness |

|--------------------|----------|---------|-----------|------------|---------------|---------------|-----------|

| MT29F512G08EBLEEJ4 | 1        | 512Gb   | 1         | 1          | Common        | 132-ball VBGA | 1.0 mm    |

| MT29F1T08EELEEJ4   | 2        | 1Tb     | 2         | 2          | Separate 2 CH | 132-ball VBGA | 1.0 mm    |

| MT29F2T08EMLEEJ4   | 4        | 2Tb     | 4         | 4          | Separate 2 CH | 132-ball VBGA | 1.0 mm    |

| MT29F4T08EULEEM4   | 8        | 4Tb     | 4         | 4          | Separate 2 CH | 132-ball LBGA | 1.3 mm    |

| MT29F8T08EWLEEM5   | 16       | 8Tb     | 4         | 4          | Separate 2 CH | 132-ball LBGA | 1.5 mm    |

# **Contents**

| Important Notes and Warnings                           |    |

|--------------------------------------------------------|----|

| General Description                                    |    |

| NV-DDR3 Signal Descriptions                            |    |

| Signal Assignments                                     |    |

| Package Dimensions                                     |    |

| Architecture                                           |    |

| Device and Array Organization                          |    |

| Bus Operation – NV-DDR3 Interface                      |    |

| Differential Signaling                                 |    |

| Warmup Cycles                                          |    |

| Warmup Cycle Restrictions                              |    |

| On-Die Termination                                     |    |

| Self-Termination On-Die Termination                    |    |

| Matrix Termination                                     |    |

| Matrix Termination Examples                            |    |

| NV-DDR3 Standby                                        |    |

| NV-DDR3 Idle                                           |    |

| NV-DDR3 Pausing/Exiting/Interrupting Data Input/Output |    |

| NV-DDR3 Commands                                       |    |

| NV-DDR3 Addresses                                      |    |

| NV-DDR3 Data Input                                     |    |

| NV-DDR3 Data Output                                    |    |

| Write Protect                                          |    |

| Ready/Busy#                                            |    |

| Device Initialization                                  |    |

| V <sub>PP</sub> Initialization                         |    |

| Volume Addressing                                      |    |

| Volume Appointment                                     |    |

| Appointing Volume Addresses                            |    |

| Selecting a Volume                                     |    |

| Multiple Volume Operation Restrictions                 |    |

| Volume Reversion                                       |    |

| Data Training                                          |    |

| DCC Training                                           |    |

| Read DQ Training                                       |    |

| Write DQ Training (Tx Side) Electronic Mirroring       |    |

| Activating Interfaces                                  |    |

| Command Definitions                                    |    |

| Reset Operations                                       |    |

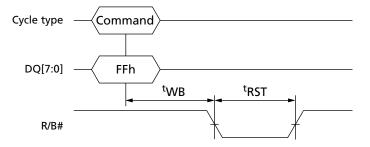

| RESET (FFh)                                            |    |

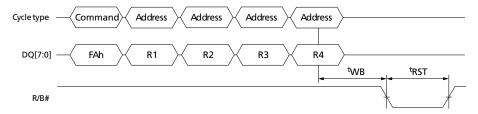

| RESET LUN (FAh)                                        |    |

| HARD RESET (FDh)                                       |    |

| Identification Operations                              |    |

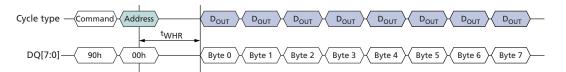

| READ ID (90h)                                          |    |

| READ ID Parameter Tables                               |    |

| READ PARAMETER PAGE (ECh)                              |    |

| Parameter Page Data Structure Tables                   |    |

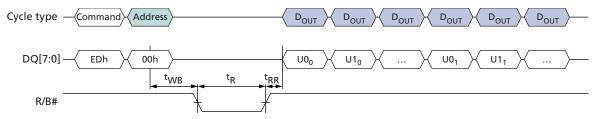

| READ UNIQUE ID (EDh)                                   |    |

| Configuration Operations                               |    |

| Feature Address Register Bit Usage Restrictions        |    |

| 1 catate radices negister bit osage nestrictions       | 50 |

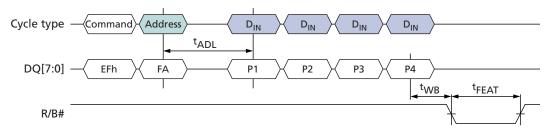

| SET FEATURES (EFh)                                            |     |

|---------------------------------------------------------------|-----|

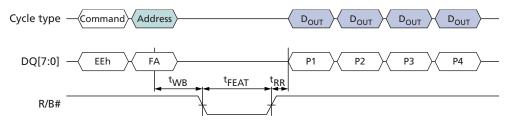

| GET FEATURES (EEh)                                            |     |

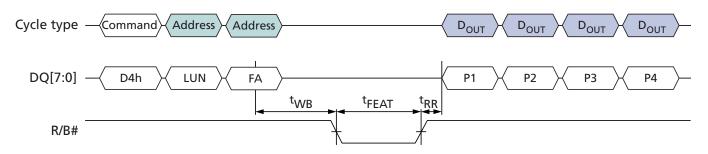

| GET/SET FEATURES by LUN (D4h/D5h)                             |     |

| Feature Address Details                                       |     |

| VOLUME SELECT (E1h)                                           |     |

| ODT CONFIGURE (E2h)                                           |     |

| ODT CONFIGURE (E2h) for LUNs Operating in Mirrored Mode       |     |

| ZQ Calibration                                                |     |

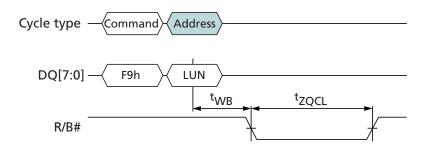

| ZQ Calibration Long (F9h)                                     |     |

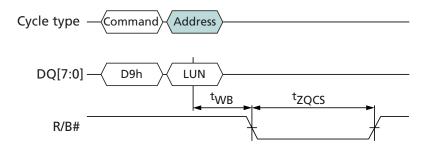

| ZQ Calibration Short (D9h)                                    |     |

| ZQ External Resistor Value, Tolerance, And Capacitive Loading |     |

| Status Operations                                             |     |

| Read Status Restrictions                                      |     |

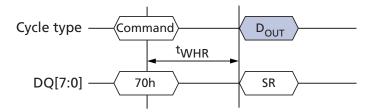

| READ STATUS (70h)                                             |     |

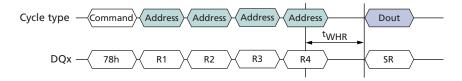

| READ STATUS ENHANCED (78h)                                    |     |

| FIXED ADDRESS READ STATUS ENHANCED (71h)                      |     |

| EXTENDED STATUS REGISTER READ (79h)                           |     |

| Column Address Operations                                     |     |

|                                                               |     |

| CHANGE READ COLUMN ENHANCED (06h-E0h)                         |     |

| CHANGE WRITE COLUMN (85h)                                     |     |

| CHANGE ROW ADDRESS (85h)                                      |     |

| Read Operations                                               |     |

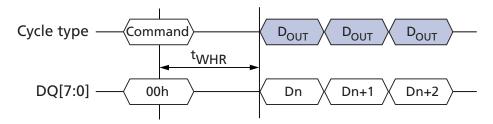

| READ MODE (00h)                                               |     |

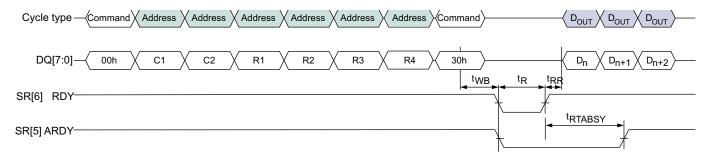

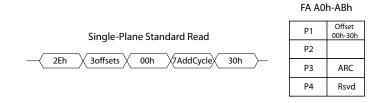

| READ PAGE (00h-30h)                                           |     |

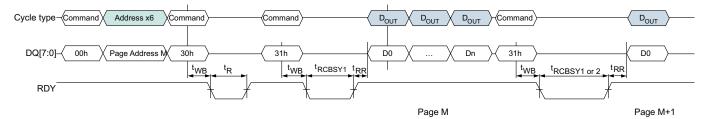

| READ PAGE (0011-3011)  READ PAGE CACHE SEQUENTIAL (31h)       |     |

| READ PAGE CACHE RANDOM (00h-31h)                              |     |

| READ PAGE CACHE LAST (3Fh)                                    |     |

| READ PAGE MULTI-PLANE (00h-32h)                               |     |

| READ OFFSET PREFIX (2Eh) Command                              |     |

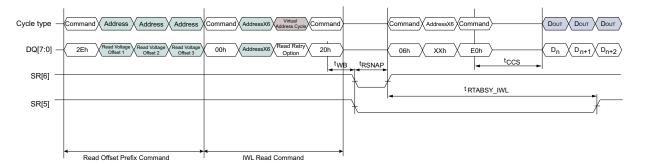

| IWL READ (00h-20h)                                            |     |

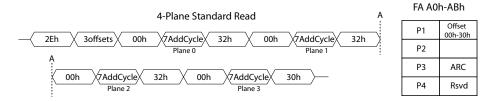

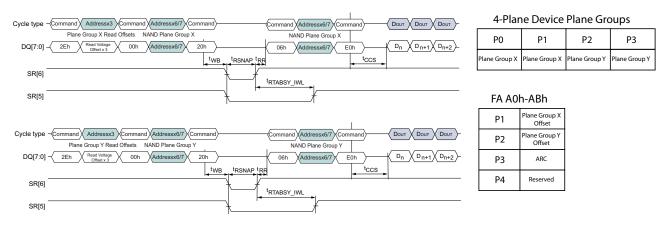

| IWL Read Feature                                              |     |

| Independent Word Line Operation                               |     |

| FEATURE ADDRESS A0h-ABh                                       |     |

| Auto Read Calibration Operations                              |     |

| Auto Read Calibration                                         |     |

| Auto Read Calibration and Read Offset Prefix                  | 166 |

| Reading out Calibrated offsets with GET FEATURES (EEh/D4h)    |     |

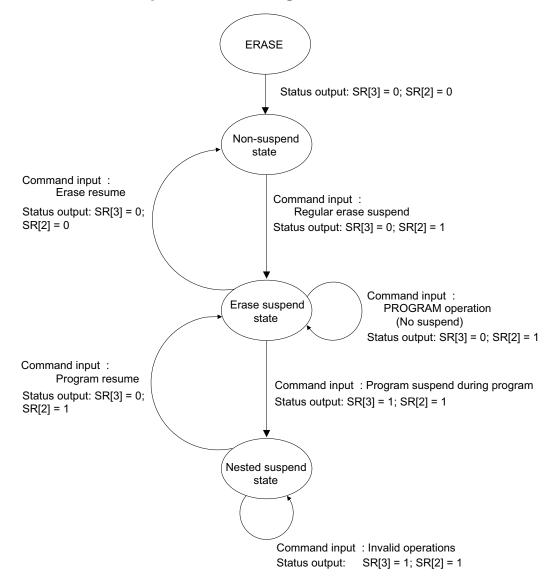

| Address Cycle Read Retry (ACRR) Operations                    | 167 |

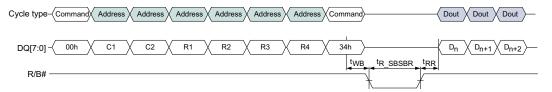

| Single Bit Soft Bit Read Operations                           |     |

| SINGLE BIT SOFT BIT READ PAGE (00h-34h)                       |     |

| SLC Operations                                                | 171 |

| Configuration using SLC MODE LUN ENABLE (3Bh) with Auto Exit  | 171 |

| SLC/TLC Mode Operations                                       | 172 |

| 3Bh Operation Guidelines                                      | 173 |

| Prefix Opcode for SLC Entry                                   |     |

| Valid Operations with SLC MODE LUN ENABLE (3Bh)               |     |

| TLC One Pass Programming                                      |     |

| PROGRAM PAGE (80h-10h)                                        |     |

| PROGRAM PAGE CACHE (80h-15h)                                  |     |

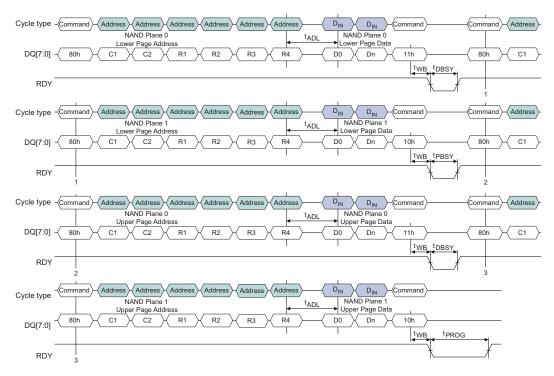

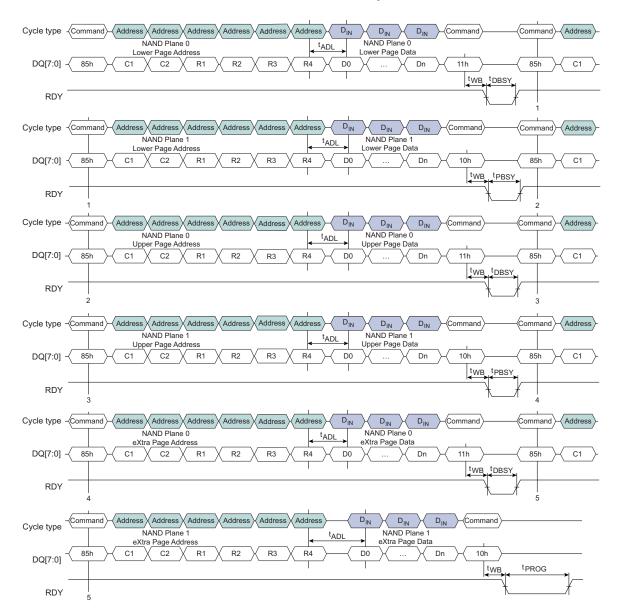

| PROGRAM PAGE MULTI-PLANE (80h-11h)                            |     |

| PROGRAM SUSPEND (84h) and PROGRAM RESUME (13h)                | 192 |

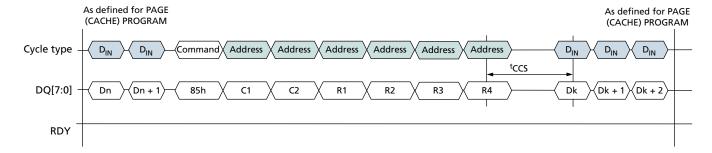

| Multiple Page Data Entry during Cache Programming                                           |       |

|---------------------------------------------------------------------------------------------|-------|

| Feature Address 7Fh: Manual Dynamic Word Line Start Voltage                                 |       |

| Erase Operations                                                                            |       |

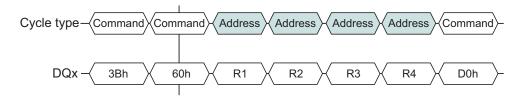

| ERASE BLOCK (60h-D0h)                                                                       |       |

| ERASE BLOCK MULTI-PLANE (60h-D1h)                                                           |       |

| ERASE BLOCK MULTI-PLANE (60h-60h-D0h)                                                       |       |

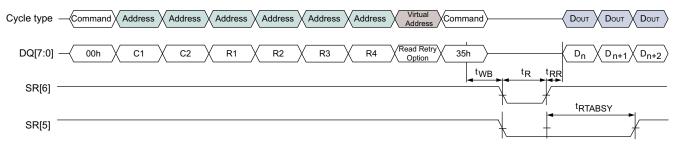

| ERASE SUSPEND (61h) and ERASE RESUME (D2h)                                                  |       |

| Nested Suspend                                                                              |       |

| Restrictions During Suspend State                                                           |       |

| TLC One Pass Copyback Operations                                                            |       |

| COPYBACK READ (00h-35h)                                                                     |       |

| COPYBACK PROGRAM (85h–10h)                                                                  |       |

| COPYBACK READ MULTI-PLANE (00h-32h)                                                         |       |

| COPYBACK PROGRAM MULTI-PLANE (85h-11h)                                                      |       |

| One-Time Programmable (OTP) Operations                                                      |       |

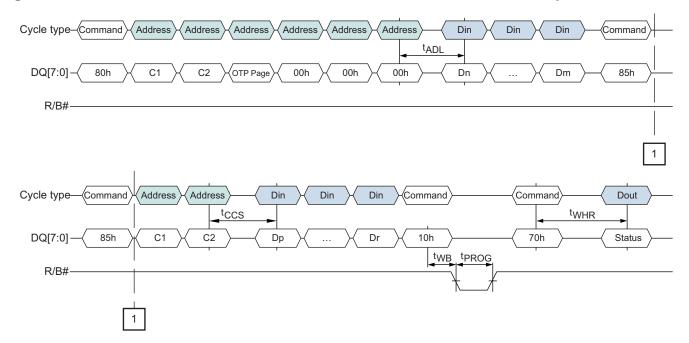

| PROGRAM OTP PAGE (80h-10h)                                                                  |       |

| PROTECT OTP AREA (80h-10h)                                                                  |       |

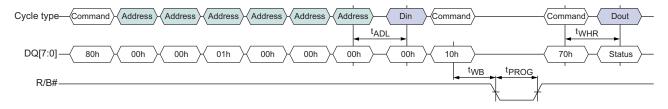

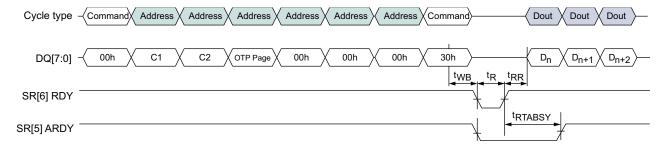

| READ OTP PAGE (00h-30h)                                                                     |       |

| Multi-Plane Operations                                                                      |       |

| Multi-Plane Addressing                                                                      |       |

| Interleaved Die (Multi-LUN) Operations                                                      |       |

| Error Management                                                                            |       |

| External Data Randomization                                                                 |       |

| Shared Pages - TLC                                                                          |       |

| Output Drive Impedance (NV-DDR3)                                                            |       |

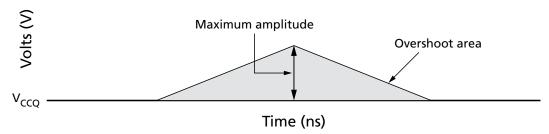

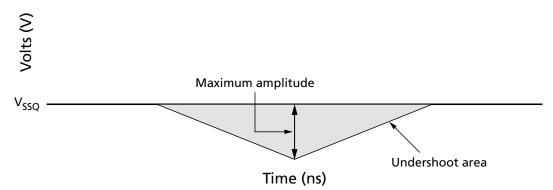

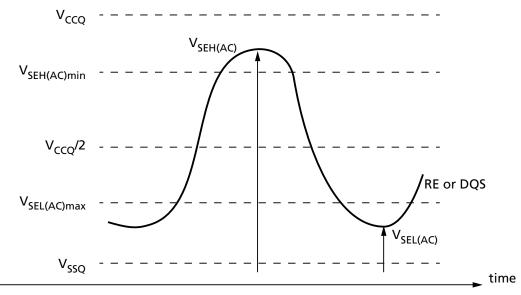

| AC Overshoot/Undershoot Specifications                                                      |       |

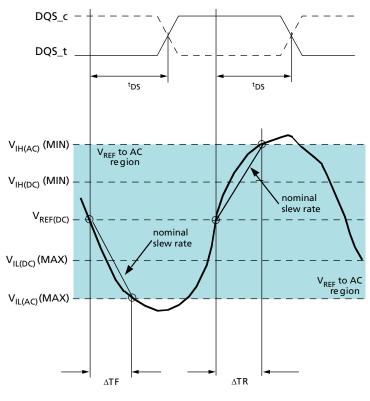

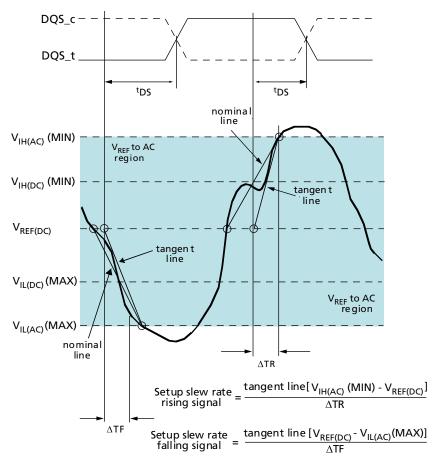

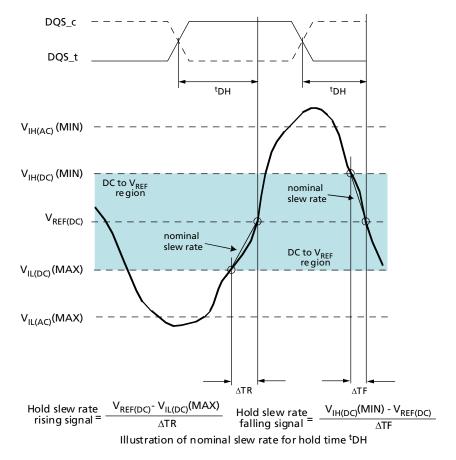

| Input Slew Rate                                                                             |       |

| Output Slew Rate                                                                            |       |

| Power Cycle and Ramp Requirements                                                           |       |

| Electrical Specifications                                                                   |       |

| Package Electrical Specification and Pad Capacitance                                        |       |

| Electrical Specifications – DC Characteristics and Operating Conditions (NV-DDR3)           |       |

| Electrical Specifications – DC Characteristics and Operating Conditions (V <sub>CCQ</sub> ) |       |

| Single-Ended Requirements for Differential Signals                                          | . 250 |

| Electrical Specifications – AC Characteristics and Operating Conditions (NV-DDR3)           |       |

| Electrical Specifications – Array Characteristics                                           |       |

| NV-DDR3 Interface Timing Diagrams                                                           |       |

| Revision History                                                                            |       |

| Rev. L – 08/26/21                                                                           |       |

| Rev. K – 3/10/21                                                                            |       |

| Rev. J – 12/23/20                                                                           |       |

| Rev. I – 11/20/20                                                                           |       |

| Rev. H – 09/30/20                                                                           |       |

| Rev. G – 07/30/20                                                                           |       |

| Rev. F – 06/30/20                                                                           |       |

| Rev. E – 05/25/20                                                                           |       |

| Rev. D – 04/10/20                                                                           |       |

| Rev. C – 02/12/20                                                                           |       |

| Rev. B – 11/20/19                                                                           |       |

| Rev. A – 11/04/19                                                                           | . 321 |

|                                                                                             |       |

|       | •  |            |   |   |

|-------|----|------------|---|---|

|       | of | <br>$\sim$ |   | 2 |

| <br>• |    |            |   |   |

|       | •  | <br>•      | • |   |

|       |    | _          |   |   |

| Figure 1: Part Numbering Information                                                        |                |

|---------------------------------------------------------------------------------------------|----------------|

| Figure 2: B47R Part Numbering Summary Table                                                 |                |

| Figure 3: 132-ball BGA (Ball-Down, Top View)                                                | 16             |

| Figure 4: 132-Ball VBGA – 12mm x 18mm x 1.0 (Package Code: J4)                              | 17             |

| Figure 5: 132-Ball LBGA – 12mm x 18mm x 1.3 (Package Code: M4)                              | 18             |

| Figure 6: 132-Ball LBGA – 12mm x 18mm x 1.5 (Package Code: M5)                              | 19             |

| Figure 7: NAND Flash Die (LUN) Functional Block Diagram                                     | 20             |

| Figure 8: Device Organization for Single-Die Package (132-ball BGA)                         | 21             |

| Figure 9: Device Organization for Two-Die Package (132-ball BGA)                            |                |

| Figure 10: Device Organization for Four-Die Package (132-ball BGA)                          | 22             |

| Figure 11: Device Organization for Eight-Die Package (132-ball BGA)                         |                |

| Figure 12: Device Organization for Sixteen-Die Package (132-ball BGA)                       |                |

| Figure 13: Array Organization per Logical Unit (LUN) for B47R in TLC mode                   |                |

| Figure 14: Array Organization per Logical Unit (LUN) for B47R in SLC mode                   |                |

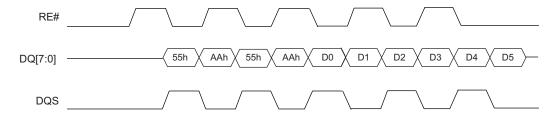

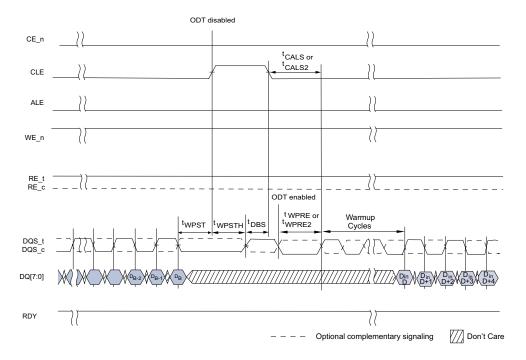

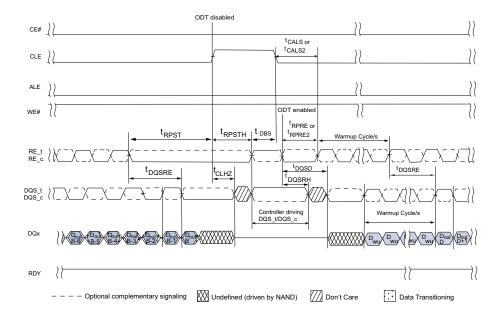

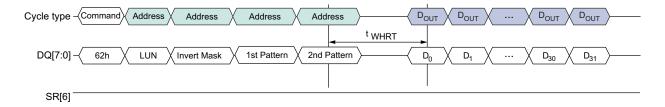

| Figure 15: Warmup Cycles for Data Output (2 Warmup Cycles)                                  |                |

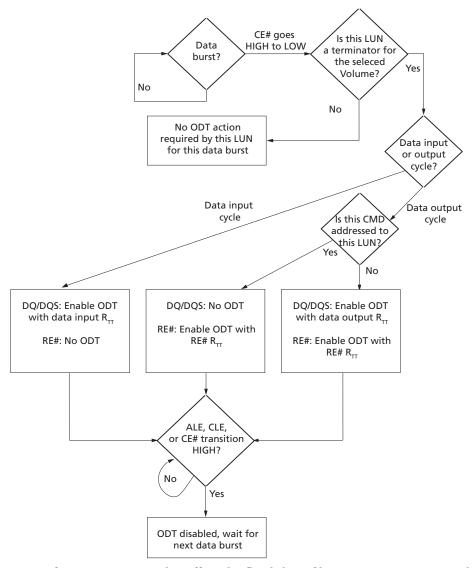

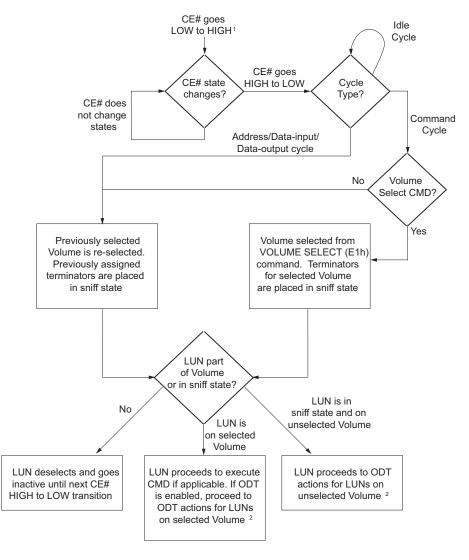

| Figure 16: Self-Termination Only ODT Behavioral Flow                                        |                |

| Figure 17: ODT Actions for LUNs on Selected Volume                                          |                |

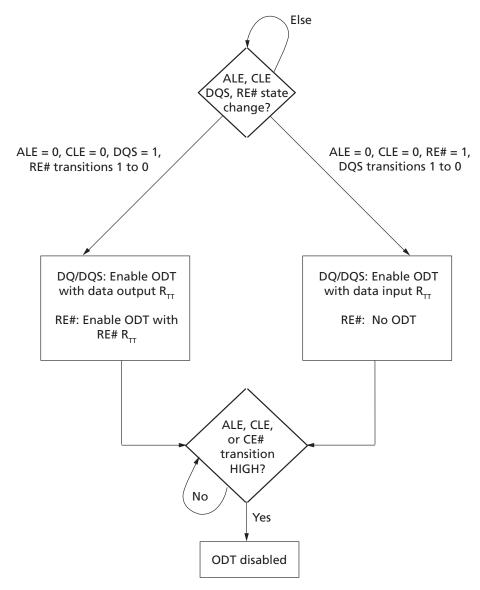

| Figure 18: ODT Actions for LUNs in Sniff State on Unselected Volume                         | 36             |

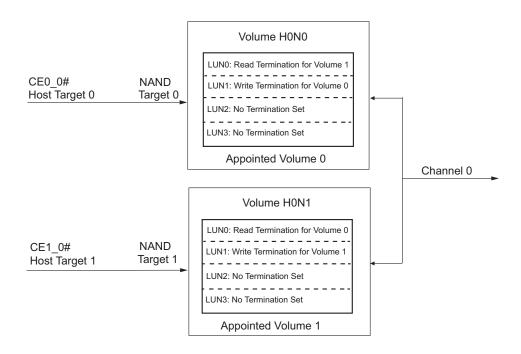

| Figure 19: Non-Target ODT for Data Output, Target ODT for Data Input Configuration Example  |                |

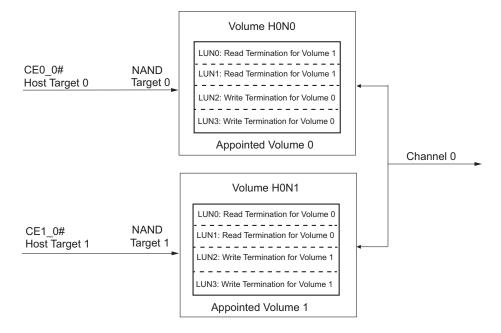

| Figure 20: Parallel Non-Target ODT Configuration Example                                    |                |

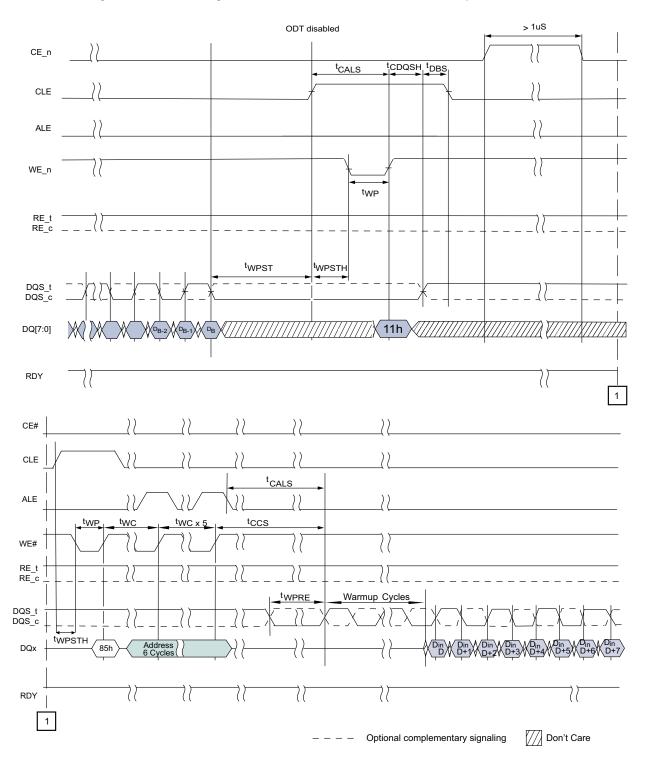

| Figure 21: Data Input Burst Exit with CLE HIGH and Resume with CLE LOW                      | 30<br>40       |

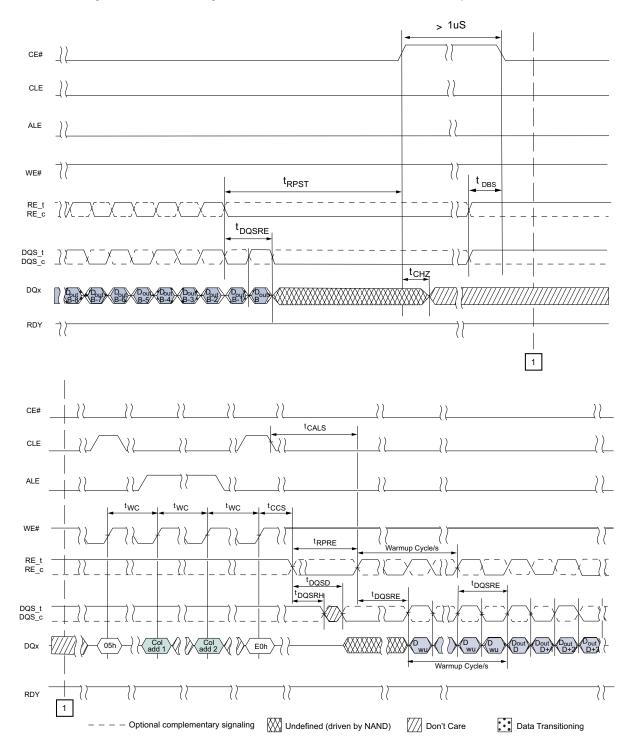

| Figure 22: Data Output Burst Exit with CLE HIGH and Resume with CLE LOW                     | <del>1</del> 0 |

| Figure 23: Data Input Burst Interruption and Resume with CE# HIGH >1µs                      |                |

| Figure 24: Data Output Burst Interruption and Resume with CE# HIGH >1µs                     |                |

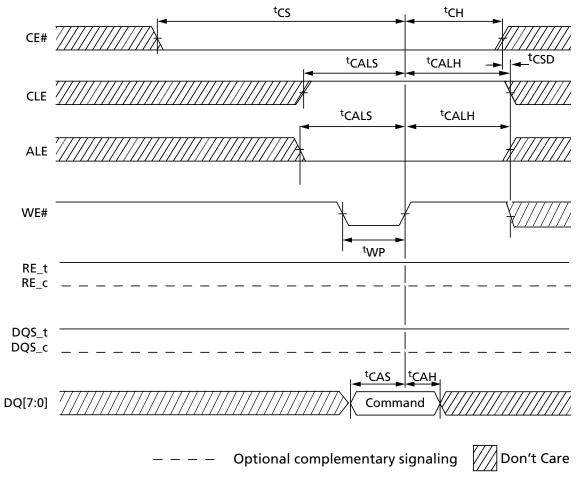

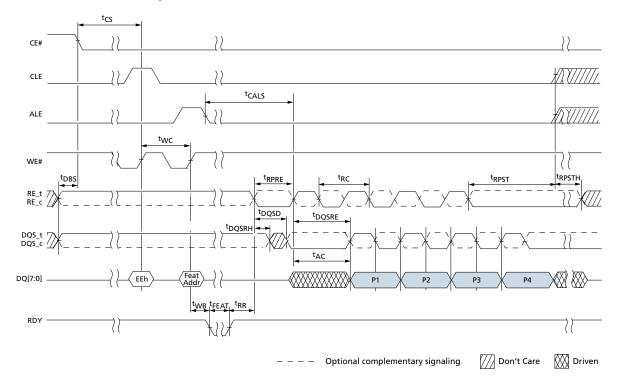

| Figure 25: NV-DDR3 Command Cycle                                                            |                |

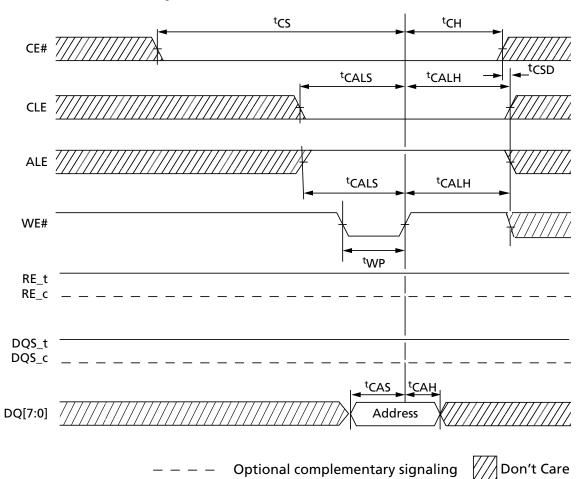

| Figure 26: NV-DDR3 Addresses Cycle.                                                         |                |

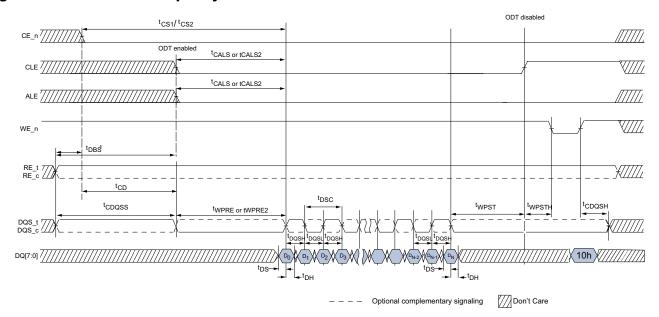

| Figure 27: NV-DDR3 Data Input Cycles                                                        |                |

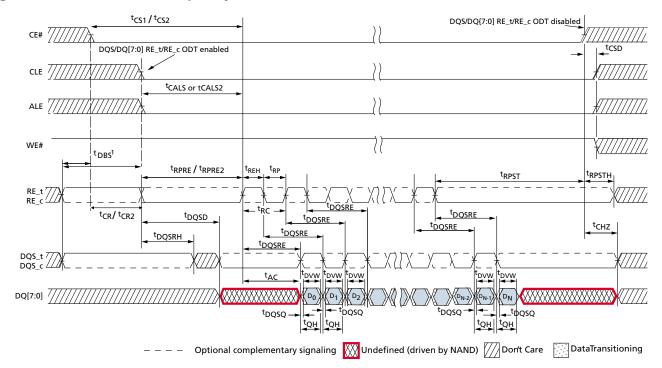

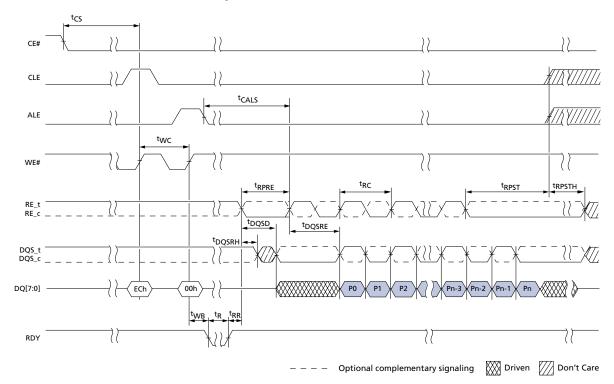

| Figure 28: NV-DDR3 Data Output Cycles                                                       |                |

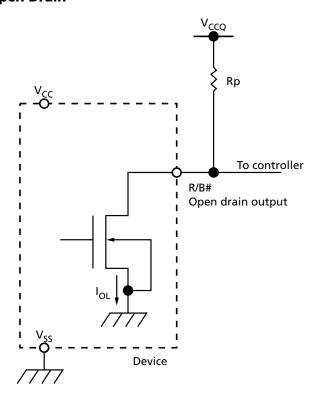

| Figure 29: READY/BUSY# Open Drain                                                           |                |

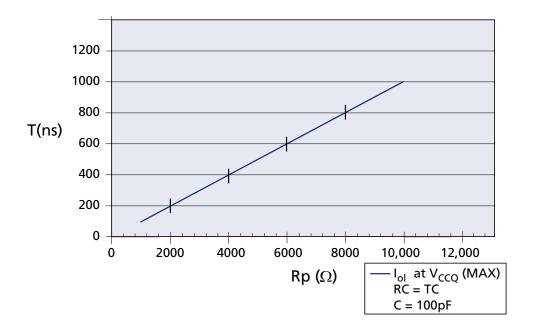

| Figure 30: TC vs R <sub>p</sub>                                                             |                |

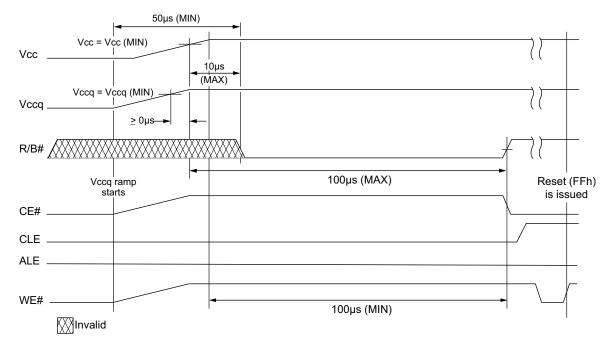

| Figure 31: Power-On Behavior                                                                |                |

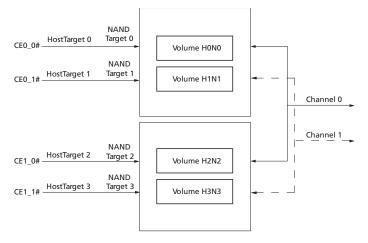

| Figure 32: Volume Addressing Assignment With Dual Channel Example                           |                |

|                                                                                             |                |

| Figure 33: Volume Reversion Behavioral Flow                                                 |                |

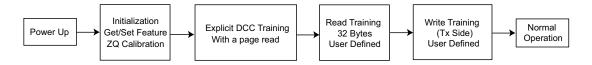

| Figure 34: Data Training Sequence Diagram                                                   |                |

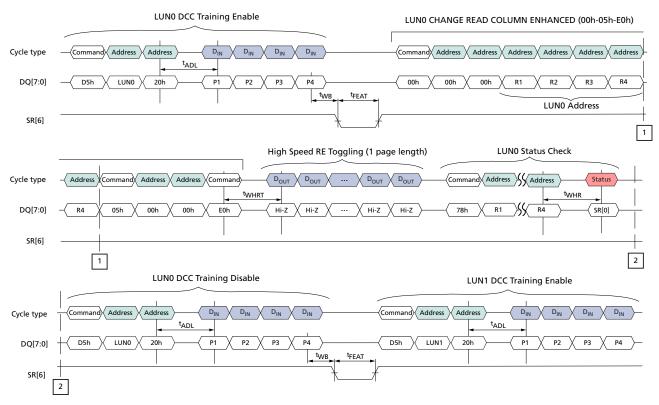

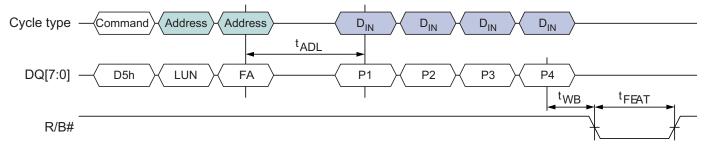

| Figure 35: Single LUN DCC Training Using SET FEATURE by LUN (D5h)                           |                |

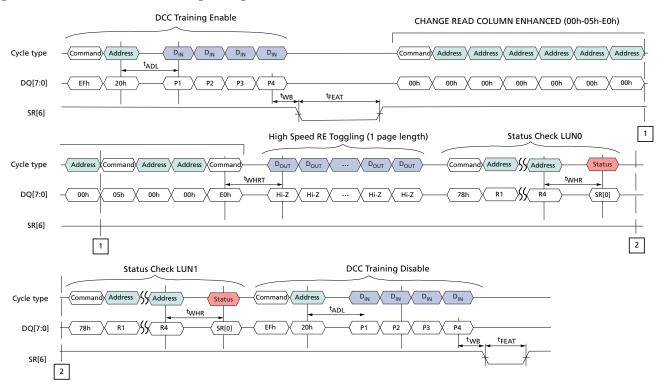

| Figure 36: Parallel DCC Training Using SET FEATURE (EFh)                                    |                |

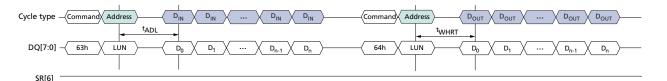

| Figure 37: Read DQ Training                                                                 |                |

| Figure 38: Write DQ Training (Tx Side)                                                      |                |

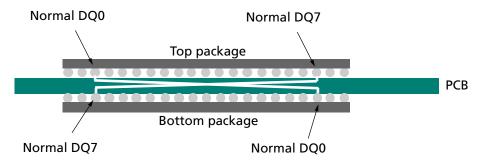

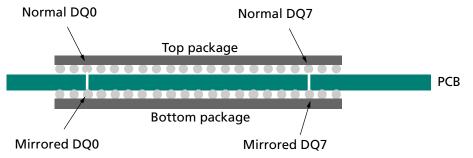

| Figure 39: Example PCB Layout of a Two-Sided System without Electronic Mirroring of DQ[7:0] |                |

| Figure 40: Example PCB Layout of a Two-Sided System with Electronic Mirroring of DQ[7:0]    |                |

| Figure 41: Example of 132-Ball BGA Package in Mirrored DQ[7:0] Pinout                       |                |

| Figure 42: RESET (FFh) Operation.                                                           |                |

| Figure 43: RESET LUN (FAh) Operation                                                        |                |

| Figure 44: HARD RESET (FDh) Operation                                                       |                |

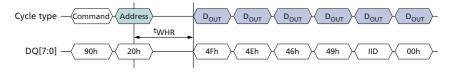

| Figure 45: READ ID (90h) with 00h Address Operation                                         |                |

| Figure 46: READ ID (90h) with 20h Address Operation                                         |                |

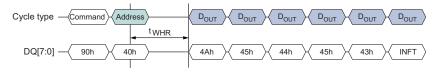

| Figure 47: READ ID (90h) with 40h Address Operation                                         |                |

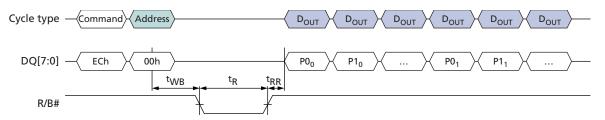

| Figure 48: READ PARAMETER (ECh) with 00h Address Operation for ONFI.                        |                |

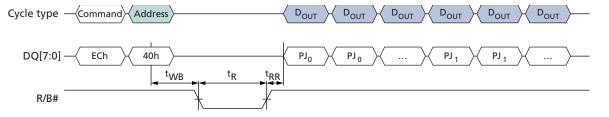

| Figure 49: READ PARAMETER (ECh) with 40h Address Operation for JEDEC                        |                |

| Figure 50: READ UNIQUE ID (EDh) Operation                                                   |                |

| Figure 51: SET FEATURES (EFh) Operation                                                     | 99             |

| Figure 52: GET FEATURES (EEh) Operation                                                            |     |

|----------------------------------------------------------------------------------------------------|-----|

| Figure 53: GET FEATURES by LUN (D4h) Operation                                                     |     |

| Figure 54: SET FEATURES by LUN (D5h) Operation                                                     | 101 |

| Figure 55: GET FEATURES by LUN (D4h) Interleaved Operation Example                                 | 102 |

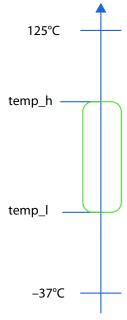

| Figure 56: Thermal Status Alert Illustration                                                       | 115 |

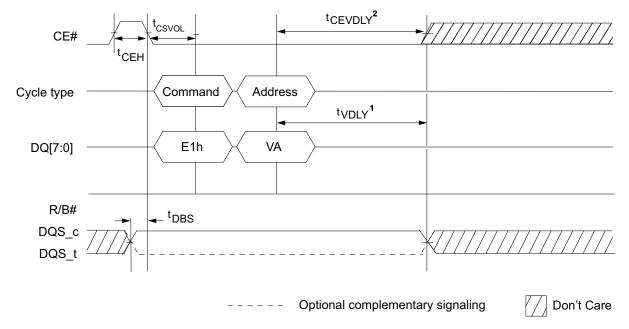

| Figure 57: VOLUME SELECT (E1h) Operation                                                           | 118 |

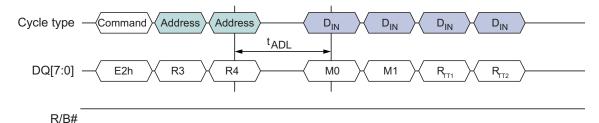

| Figure 58: ODT CONFIGURE (E2h) Operation                                                           | 119 |

| Figure 59: Calibration Time Interval Equation                                                      |     |

| Figure 60: Example of Interval Calculation between ZQCS (D9h) Commands                             |     |

| Figure 61: ZQ Calibration Long (F9h)                                                               |     |

| Figure 62: ZQ Calibration Short (D9h)                                                              |     |

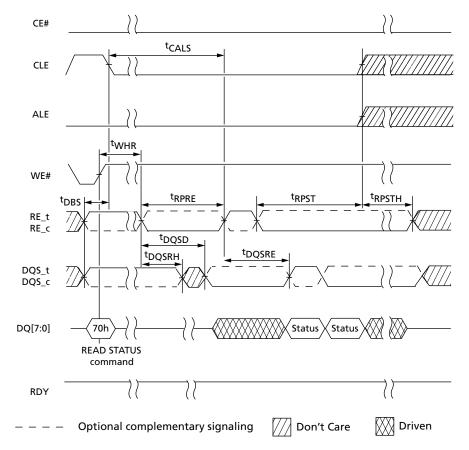

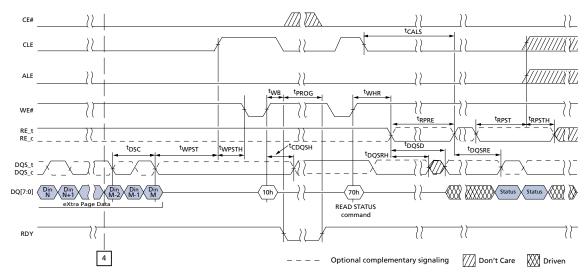

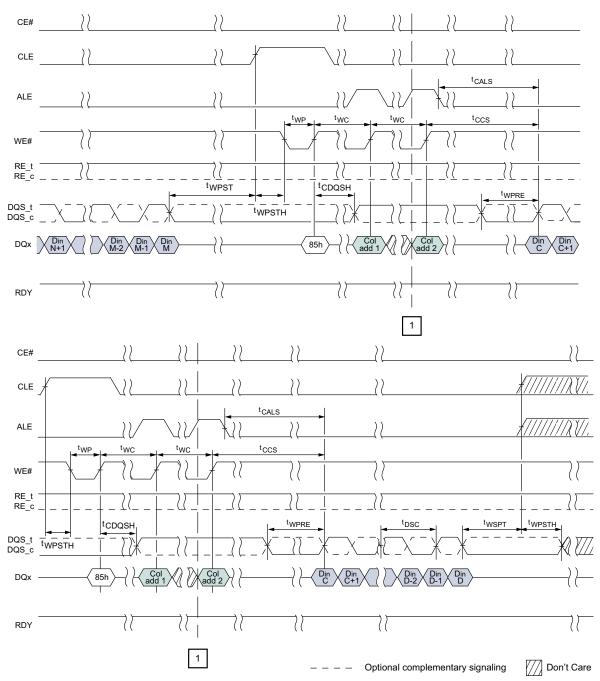

| Figure 63: READ STATUS (70h) Operation                                                             |     |

| Figure 64: READ STATUS ENHANCED (78h) Operation                                                    | 132 |

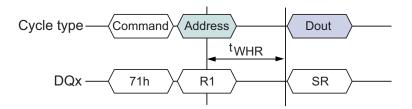

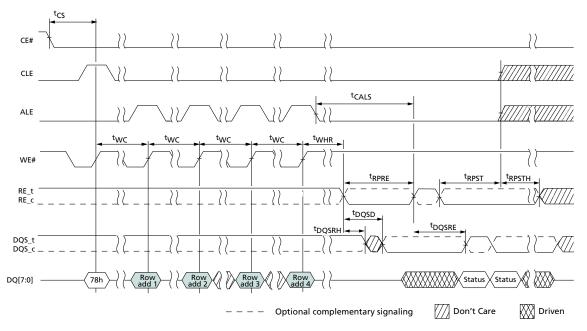

| Figure 65: FIXED ADDRESS READ STATUS ENHANCED (71h) Operation                                      | 133 |

| Figure 66: EXTENDED STATUS REGISTER READ (79h) Operation                                           | 134 |

| Figure 67: CHANGE READ COLUMN (05h-E0h) Operation                                                  |     |

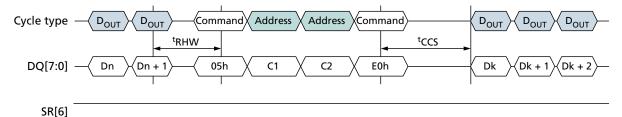

| Figure 68: CHANGE READ COLUMN ENHANCED (06h-E0h) Operation                                         | 135 |

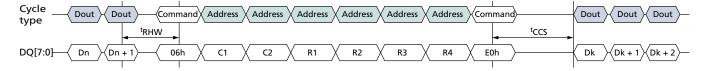

| Figure 69: CHANGE READ COLUMN ENHANCED (00h-05h-E0h) Operation                                     |     |

| Figure 70: CHANGE WRITE COLUMN (85h) Operation                                                     | 136 |

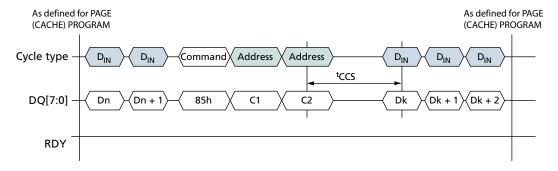

| Figure 71: CHANGE ROW ADDRESS (85h) Operation                                                      | 137 |

| Figure 72: READ MODE (00h) Operation                                                               | 142 |

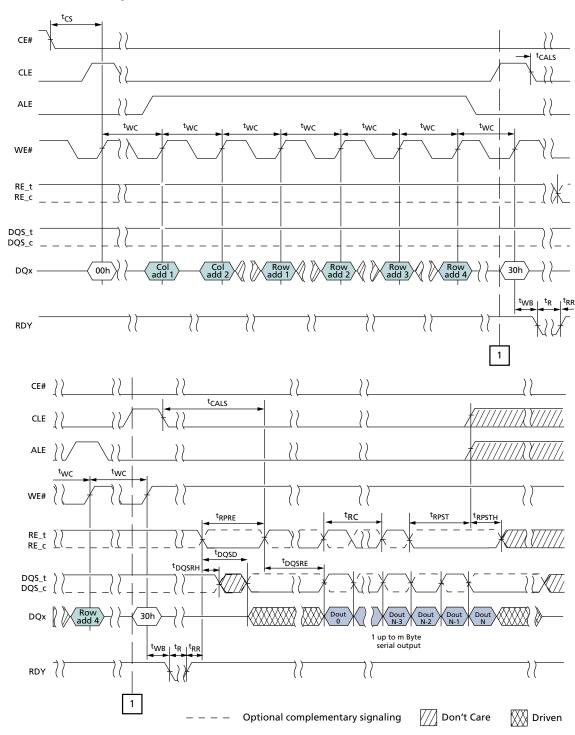

| Figure 73: READ PAGE (00h-30h) Operation                                                           | 143 |

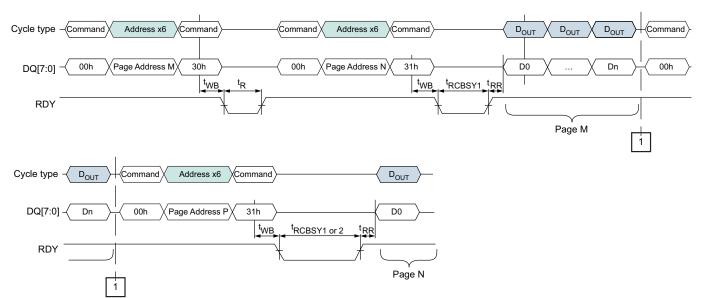

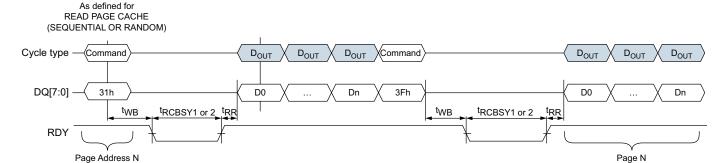

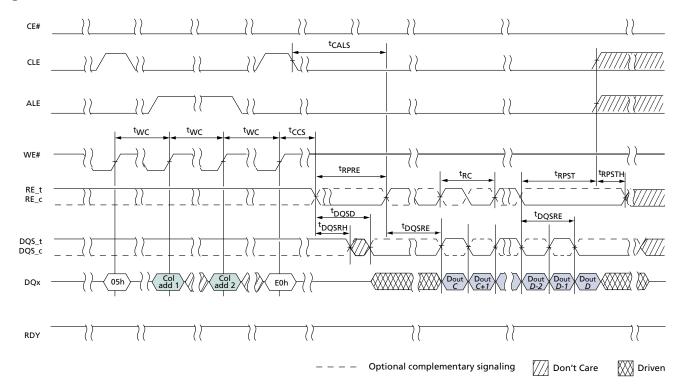

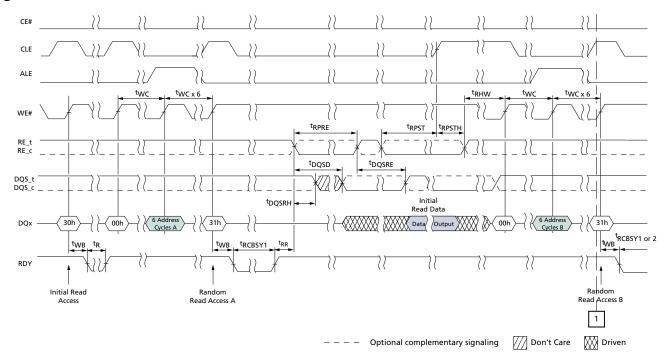

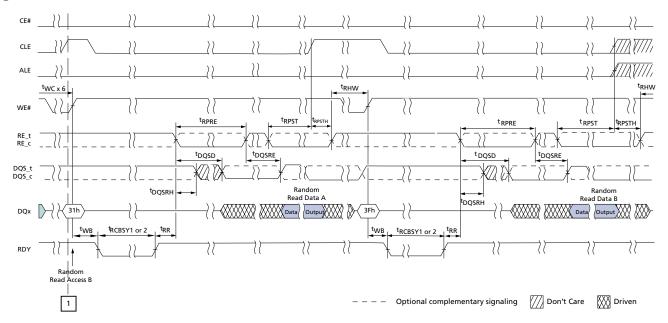

| Figure 74: READ PAGE CACHE SEQUENTIAL (31h) Operation                                              | 144 |

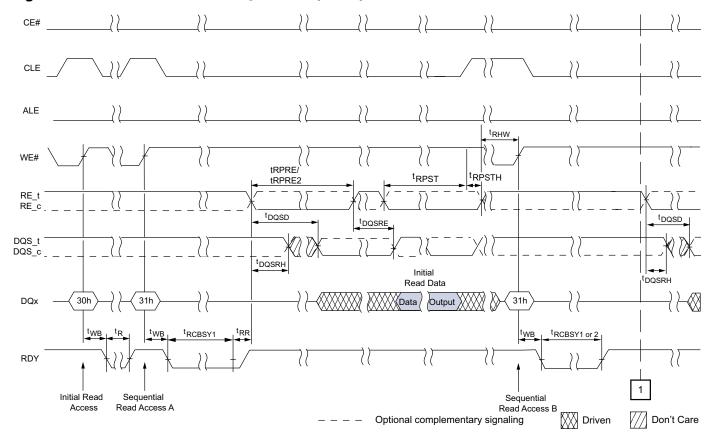

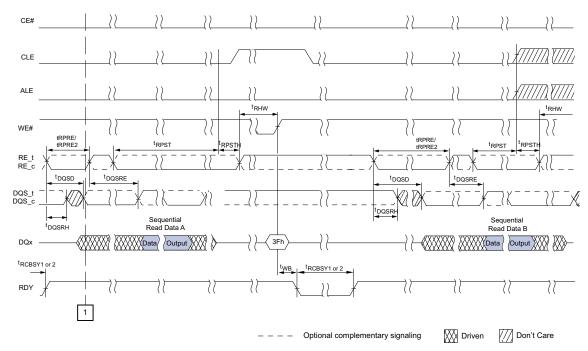

| Figure 75: READ PAGE CACHE RANDOM (00h-31h) Operation                                              | 145 |

| Figure 76: READ PAGE CACHE LAST (3Fh) Operation                                                    | 146 |

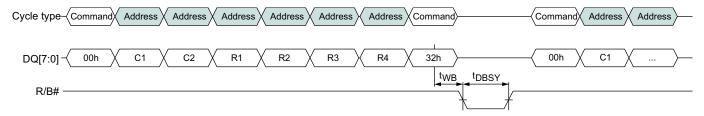

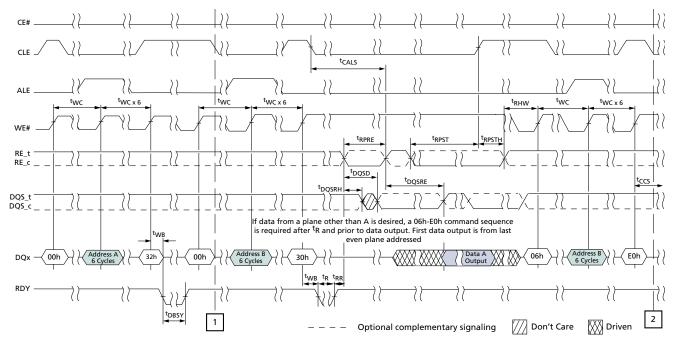

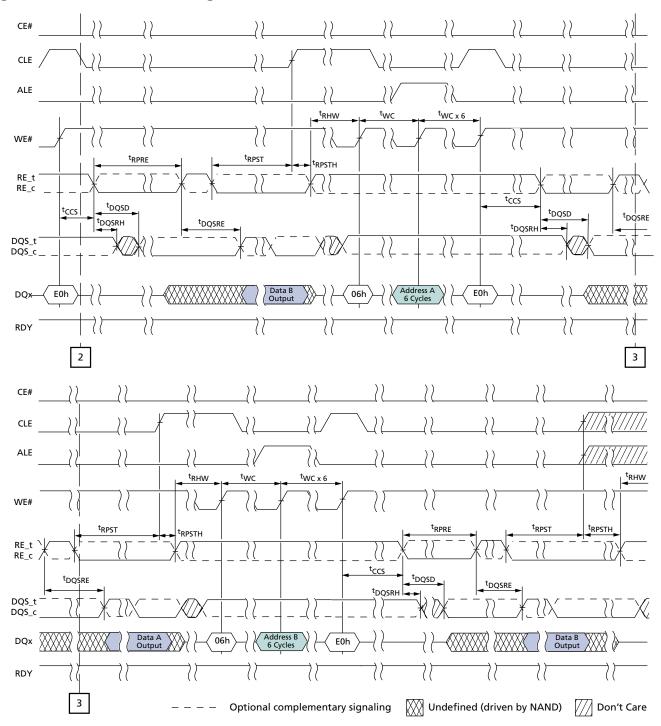

| Figure 77: READ PAGE MULTI-PLANE (00h-32h) Operation                                               | 147 |

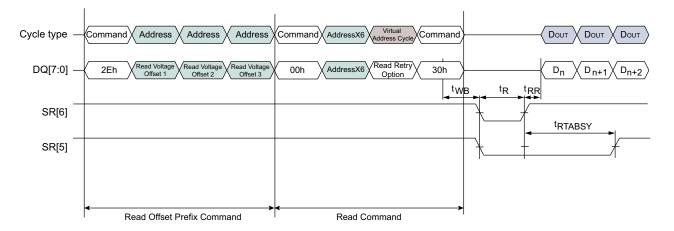

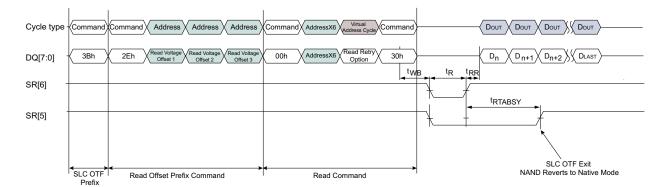

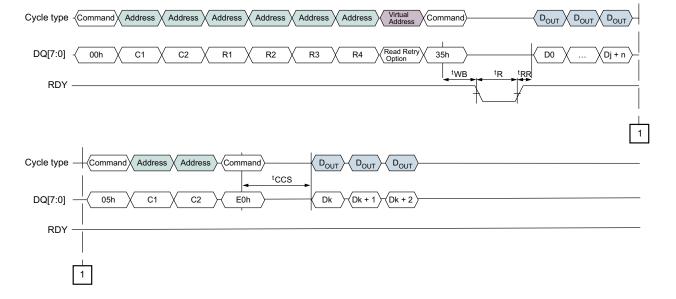

| Figure 78: READ OFFSET PREFIX (2Eh) Command with Read Page (00h-30h) with ACRR Enabled             | 147 |

| Figure 79: READ OFFSET PREFIX (2Eh) Command with IWL READ (00h-20h) with ACRR Enabled              | 149 |

| Figure 80: Standard Read - Single and Multiplane Offset Location                                   | 151 |

| Figure 81: IWL Read IWLx2 Offset Location                                                          |     |

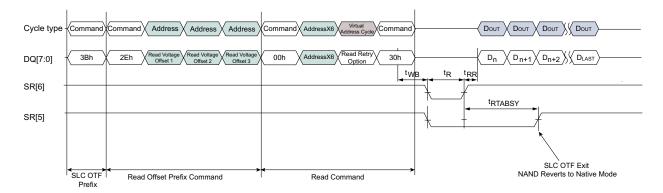

| Figure 82: READ OFFSET PREFIX (2Eh) Command during SLC OTF with ACRR Enabled                       | 153 |

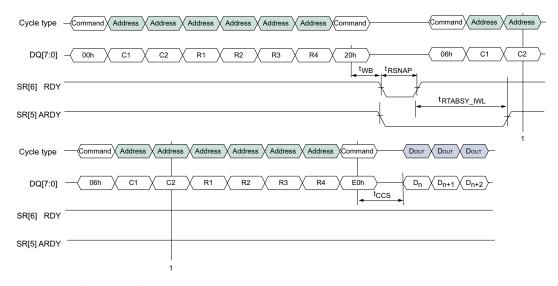

| Figure 83: IWL READ (00h-20h) Operation                                                            | 154 |

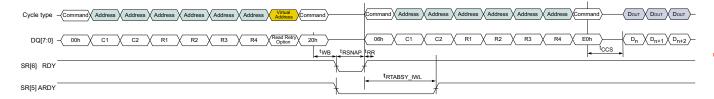

| Figure 84: IWL READ (00h-20h) Operation with ACRR Enabled                                          | 154 |

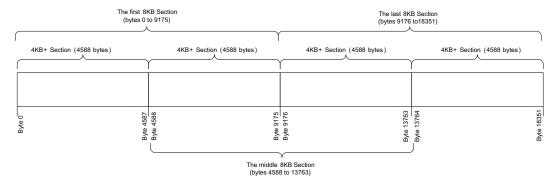

| Figure 85: Example of Fixed 8KB+ Length Sections                                                   |     |

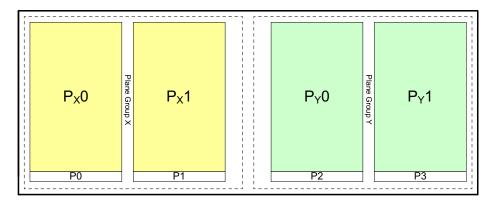

| Figure 86: Plane Group Diagram                                                                     | 155 |

| Figure 87: IWLx2 Control on 4 plane device                                                         | 156 |

| Figure 88: FEATURE ADDRESS A0h-ABh Offsets for 2 Plane Group IWL                                   | 158 |

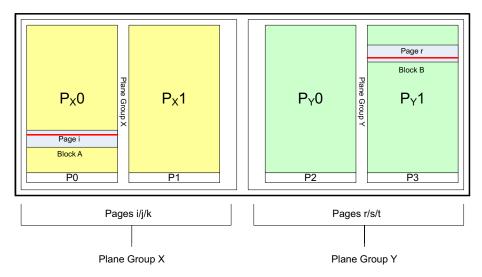

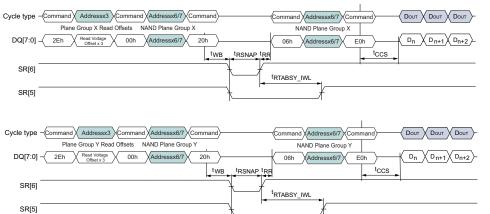

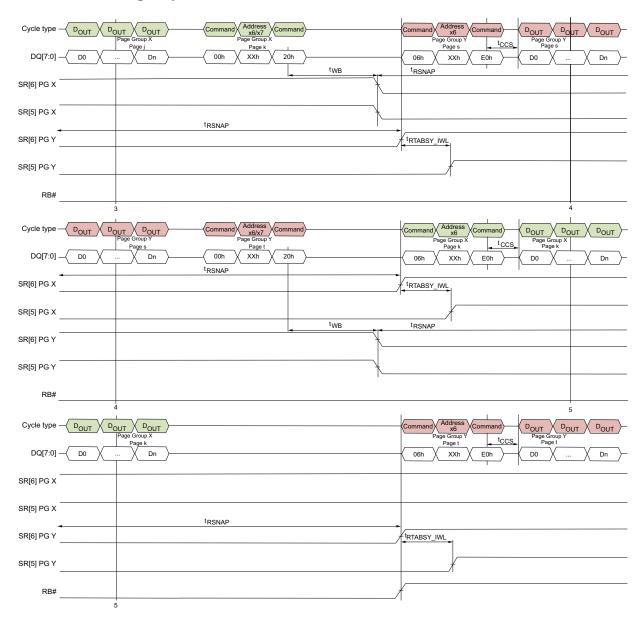

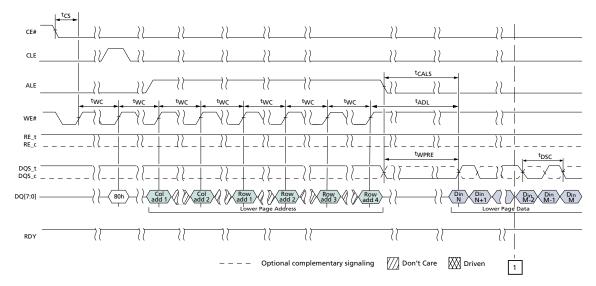

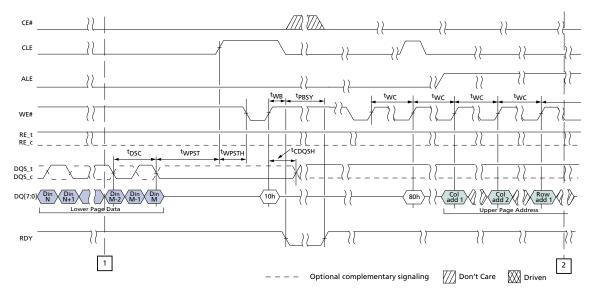

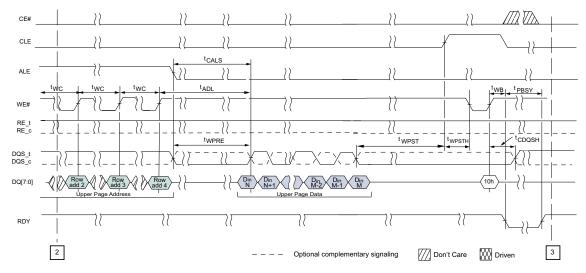

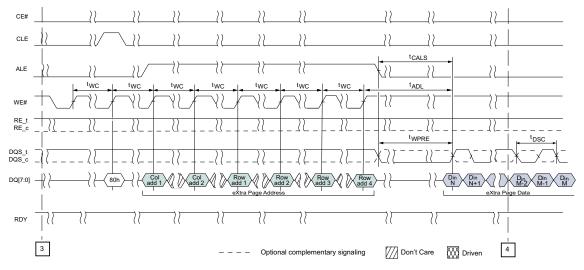

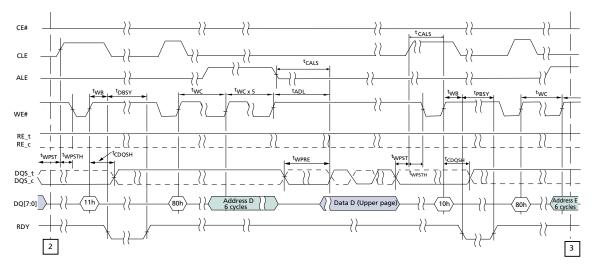

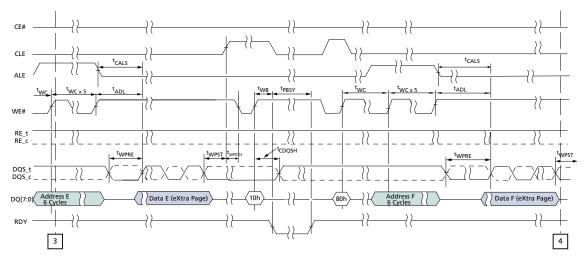

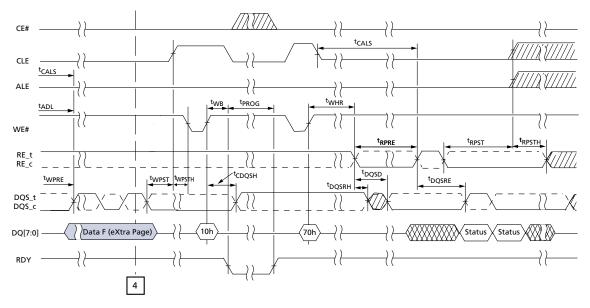

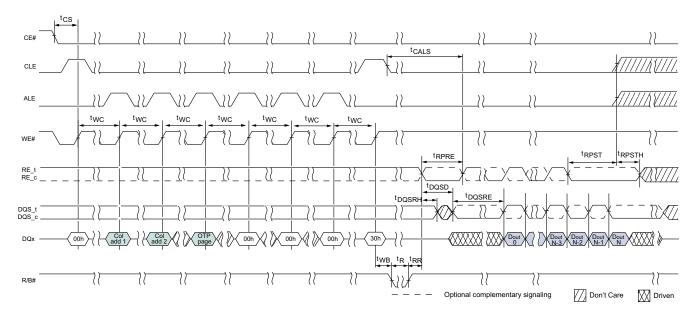

| Figure 89: IWLx2 Timing Sequence for 00h-20h (1 of 2)                                              | 159 |

| Figure 90: IWLx2 Timing Sequence for 00h-20h (2 of 2)                                              | 160 |

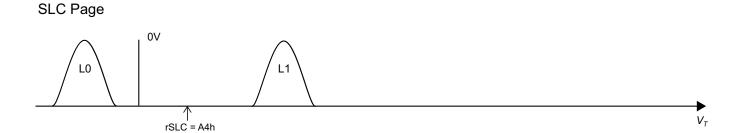

| Figure 91: Read Offset Levels for Feature Addresses A0h-ABh                                        | 163 |

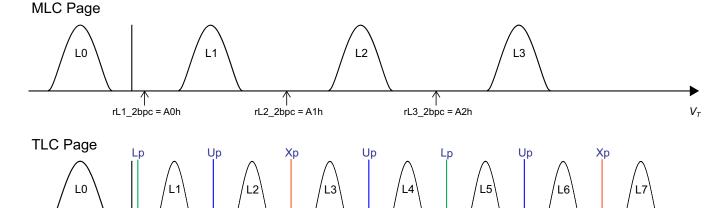

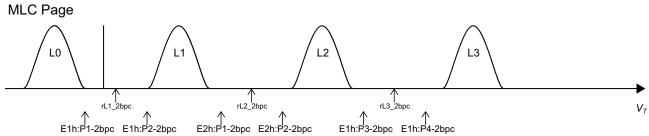

| Figure 92: SBSBR Read Offset Levels for Feature Addresses B1h-B4h, E1h-E3h                         | 169 |

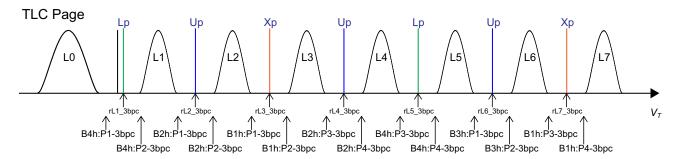

| Figure 93: SBSBR Encoding                                                                          | 170 |

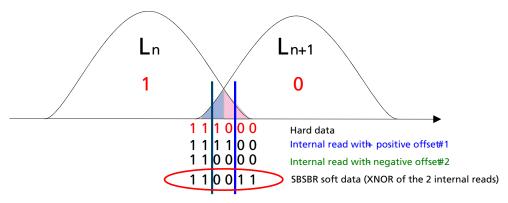

| Figure 94: SINGLE BIT SOFT BIT READ PAGE (00h-34h) Operation                                       | 171 |

| Figure 95: SLC MODE LUN ENABLE (3Bh) example with ERASE BLOCK (60h-D0h)                            | 172 |

| Figure 96: READ OFFSET PREFIX (2Eh) SLC OTF Sequence                                               | 176 |

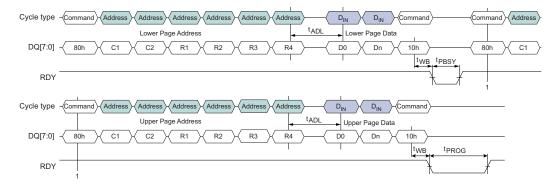

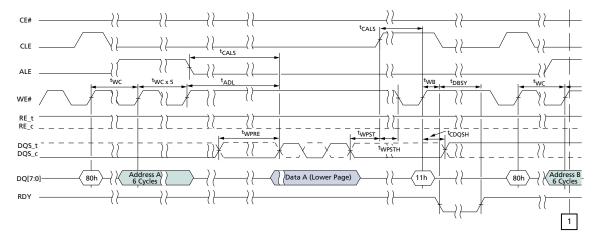

| Figure 97: PROGRAM PAGE (80h-10h) Operation with MLC Single Pass Programming                       | 181 |

| Figure 98: Two-Plane PROGRAM PAGE MULTI-PLANE (80h-11h) Operation with MLC Single Pass Programming |     |

| 181                                                                                                | Ü   |

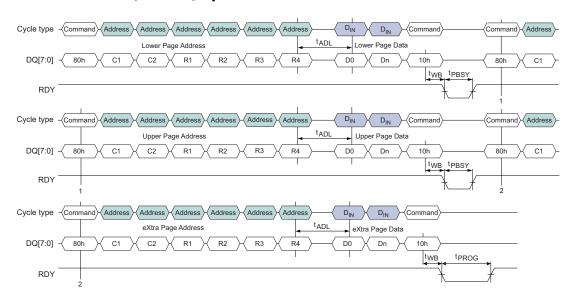

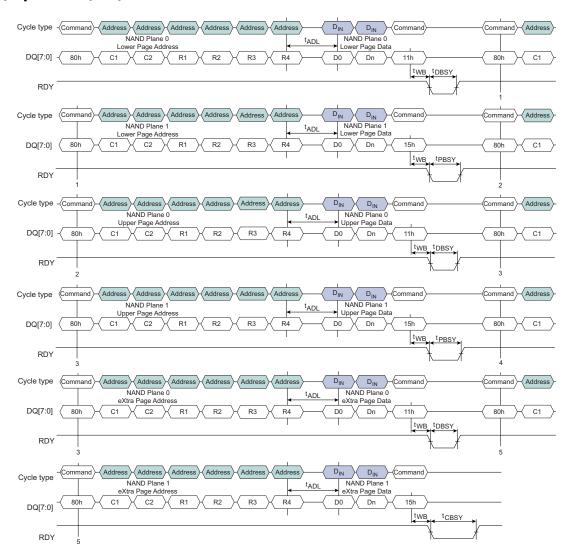

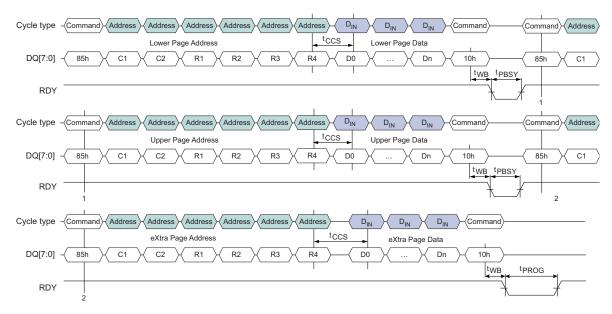

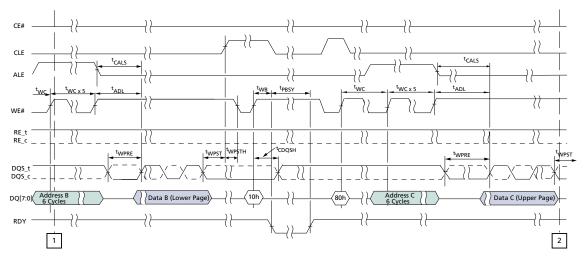

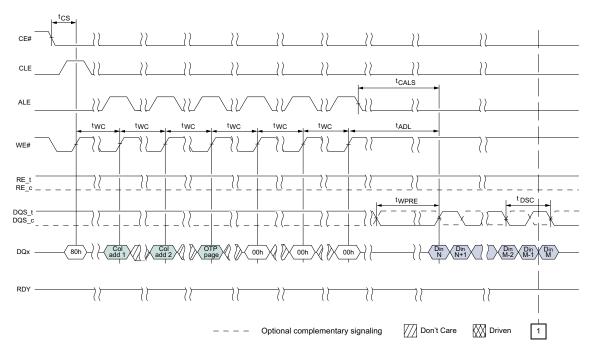

| Figure 99: PROGRAM PAGE (80h-10h) Operation - TLC One Pass                                         | 183 |

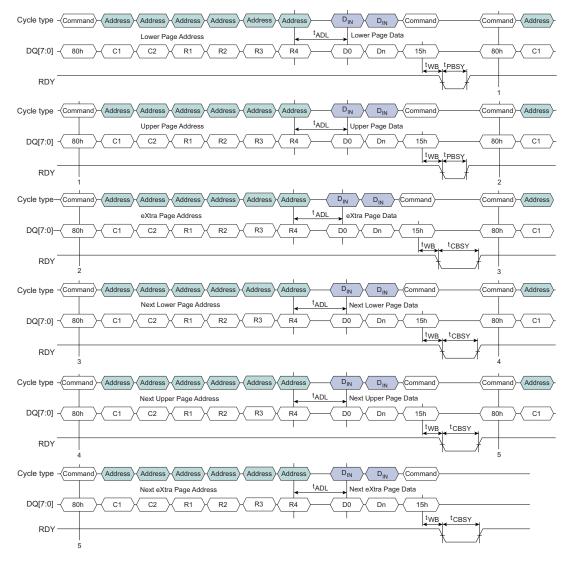

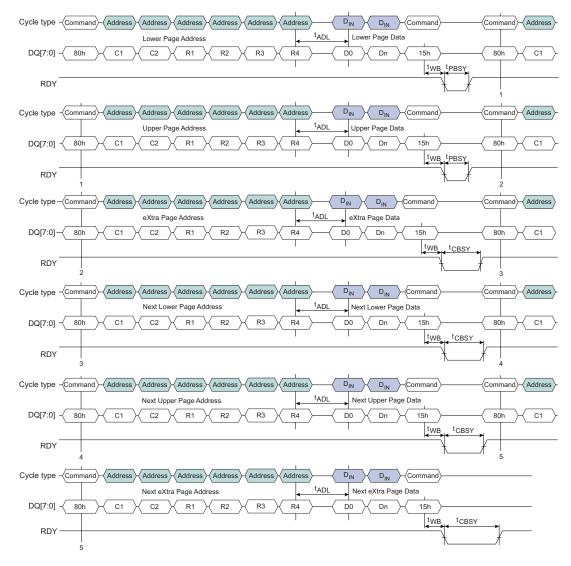

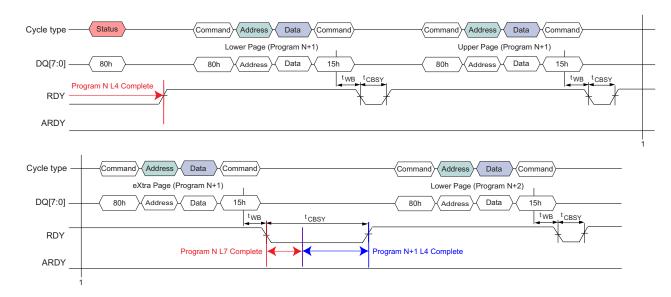

| Figure 100: PROGRAM PAGE CACHE (80h-15h) Operation (Start) - TLC One Pass                          |     |

| Figure 101: PROGRAM PAGE CACHE (80h-15h) Operation (End) - TLC One Pass                            |     |

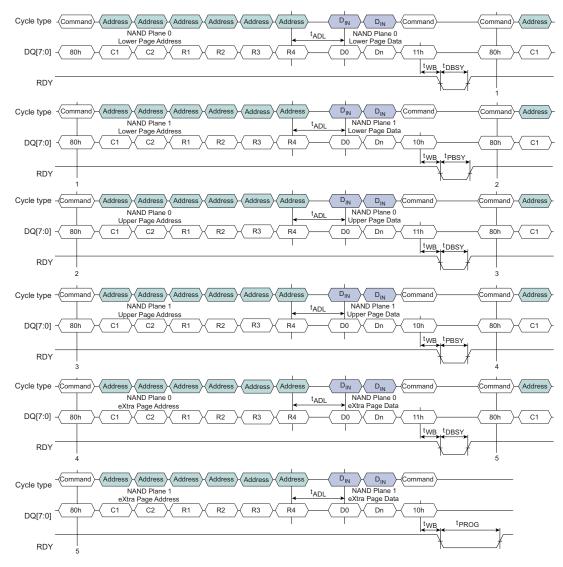

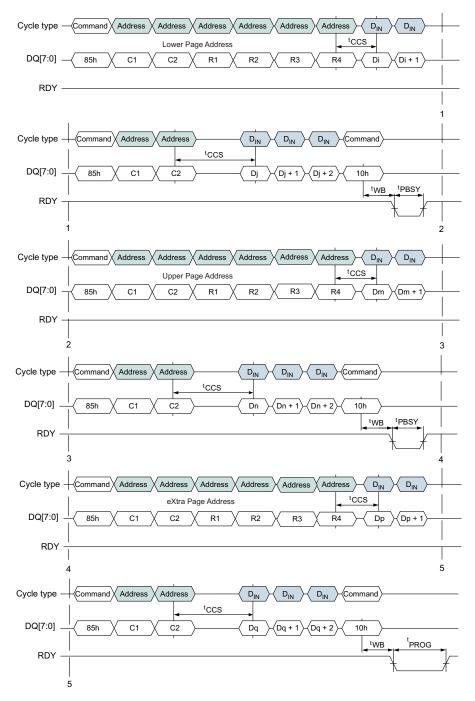

| Figure 102: Two-Plane PROGRAM PAGE MULTI-PLANE (80h-11h) Operation - TLC One Pass                  |     |

| Figure 103: Two-Plane PROGRAM PAGE MULTI-PLANE (80h-11h) with PROGRAM PAGE CACHE (80h-15h) Ope     |     |

| tion (End) - TLC One Pass                                                                                 | . 191 |

|-----------------------------------------------------------------------------------------------------------|-------|

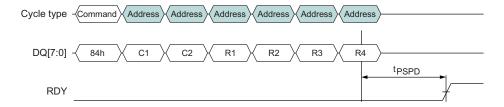

| Figure 104: PROGRAM SUSPEND (84h) Operation                                                               |       |

| Figure 105: PROGRAM RESUME (13h) Operation                                                                | . 194 |

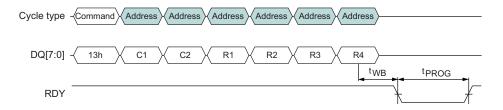

| Figure 106: Multiple Page Data Entry during Cache Programming                                             | . 194 |

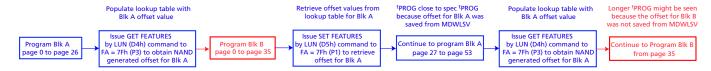

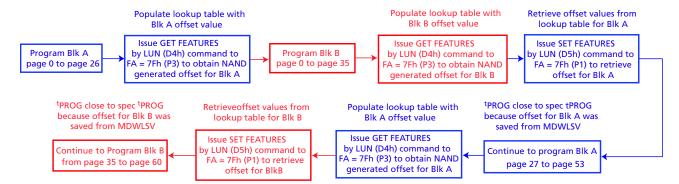

| Figure 107: Example Sequence for Programming between Blk A and Blk B - MDWLSV only Storing Offset for Blk | κA.   |

| 196                                                                                                       |       |

| Figure 108: Example Sequence for Programming between Blk A and Blk B - MDWLSV Storing Offsets for both B  | lk A  |

| and Blk B                                                                                                 |       |

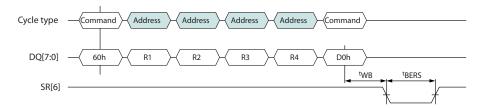

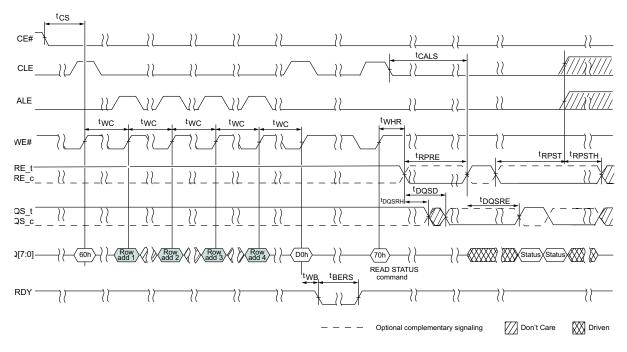

| Figure 109: ERASE BLOCK (60h-D0h) Operation                                                               | . 198 |

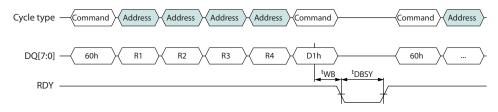

| Figure 110: ERASE BLOCK MULTI-PLANE (60h–D1h) Operation                                                   |       |

| Figure 111: ERASE BLOCK MULTI-PLANE (60h–60h-D0h) Operation.                                              |       |

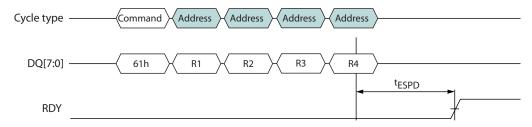

| Figure 112: ERASE SUSPEND (61h) Operation.                                                                |       |

| Figure 113: ERASE RESUME (D2h) Operation                                                                  |       |

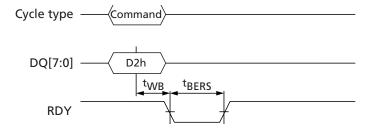

| Figure 114: NESTED SUSPEND Operation - State Diagram                                                      |       |

| Figure 115: COPYBACK READ (00h-35h) Operation                                                             | . 208 |

| Figure 116: COPYBACK READ (00h–35h) with CHANGE READ COLUMN (05h–E0h) Operation                           | . 208 |

| Figure 117: COPYBACK PROGRAM (85h–10h) Operation                                                          |       |

| Figure 118: COPYBACK PROGRAM (85h-10h) with CHANGE WRITE COLUMN (85h) Operation - TLC One Pass            | :210  |

| Figure 119: COPYBACK PROGRAM MULTI-PLANE (85h-11h) Operation - TLC One Pass:                              |       |

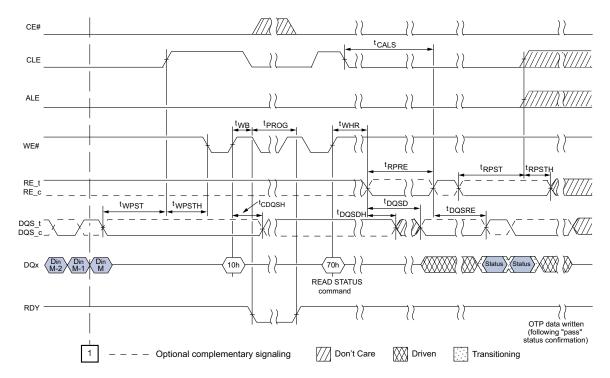

| Figure 120: PROGRAM OTP PAGE (80h-10h) Operation                                                          | . 214 |

| Figure 121: PROGRAM OTP PAGE (80h-10h) with CHANGE WRITE COLUMN (85h) Operation                           |       |

| Figure 122: PROTECT OTP AREA (80h-10h) Operation                                                          |       |

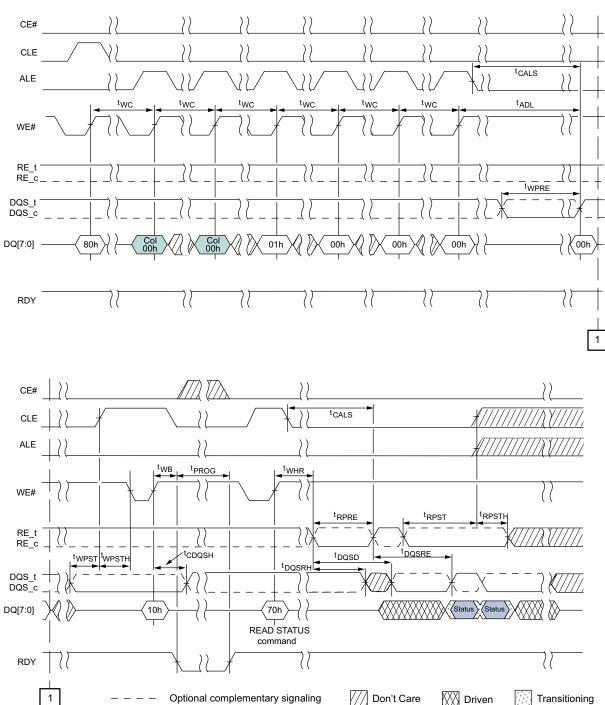

| Figure 123: READ OTP PAGE (00h-30h) Operation                                                             |       |

| Figure 124: Overshoot                                                                                     |       |

| Figure 125: Undershoot                                                                                    | . 231 |

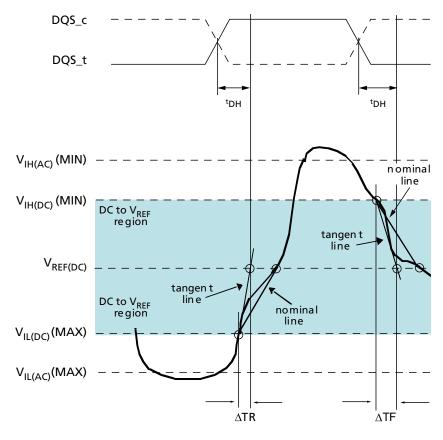

| Figure 126: Nominal Slew Rate for Data Setup Time ( <sup>t</sup> DS)                                      | . 234 |

| Figure 127: Tangent Line for Data Setup Time ( <sup>t</sup> DS)                                           | . 235 |

| Figure 128: Nominal Slew Rate for Data Hold Time ( <sup>t</sup> DH)                                       | . 236 |

| Figure 129: Tangent Line for Data Hold Time ( <sup>t</sup> DH)                                            | . 237 |

| Figure 130: Single-Ended Requirements for Differential Signals                                            |       |

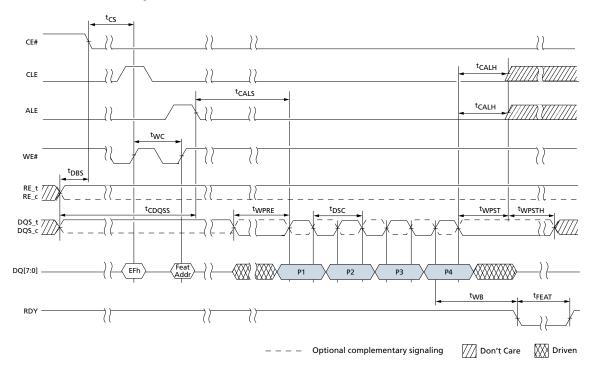

| Figure 131: SET FEATURES Operation                                                                        | . 277 |

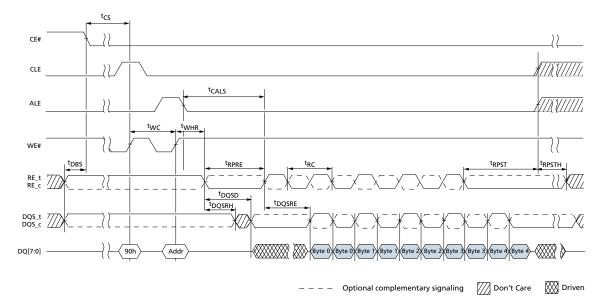

| Figure 132: READ ID Operation                                                                             |       |

| Figure 133: GET FEATURES Operation                                                                        |       |

| Figure 134: READ STATUS Cycle                                                                             |       |

| Figure 135: READ STATUS ENHANCED Operation                                                                |       |

|                                                                                                           |       |

| Figure 137: READ PAGE Operation                                                                           | . 203 |

| Figure 139: READ PAGE CACHE SEQUENTIAL (1 of 2)                                                           |       |

| Figure 140: READ PAGE CACHE SEQUENTIAL (1 of 2)                                                           |       |

| Figure 141: READ PAGE CACHE SEQUENTIAL (2 of 2)                                                           |       |

| Figure 142: READ PAGE CACHE RANDOM (1 of 2)                                                               |       |

| Figure 143: Multi-Plane Read Page (1 of 2)                                                                |       |

| Figure 144: Multi-Plane Read Page (2 of 2)                                                                |       |

| Figure 145: PROGRAM PAGE Operation (1 of 5)                                                               |       |

| Figure 146: PROGRAM PAGE Operation (2 of 5)                                                               |       |

| Figure 147: PROGRAM PAGE Operation (3 of 5)                                                               |       |

| Figure 148: PROGRAM PAGE Operation (4 of 5)                                                               |       |

| Figure 149: PROGRAM PAGE Operation (5 of 5)                                                               |       |

| Figure 150: CHANGE WRITE COLUMN                                                                           |       |

| Figure 151: Multi-Plane Program Page (1 of 5)                                                             |       |

| Figure 152: Multi-Plane Program Page (2 of 5)                                                             |       |

| Figure 153: Multi-Plane Program Page (3 of 5)                                                             |       |

| 0 0 , ,                                                                                                   |       |

| Figure 154: Multi-Plane Program Page (4 of 5) | 294 |

|-----------------------------------------------|-----|

| Figure 155: Multi-Plane Program Page (5 of 5) |     |

| Figure 156: ERASE BLOCK                       |     |

| Figure 157: READ OTP PAGE                     | 296 |

| Figure 158: PROGRAM OTP PAGE (1 of 2)         | 296 |

| Figure 159: PROGRAM OTP PAGE (2 of 2)         | 297 |

| Figure 160: PROTECT OTP AREA                  |     |

| <b>List of Tables</b> |

|-----------------------|

|-----------------------|

| Table 1: NV-DDR3 Signal Definitions                                                                         | 14    |

|-------------------------------------------------------------------------------------------------------------|-------|

| Table 2: Array Addressing for Logical Unit (LUN) for B47R in TLC mode                                       | 25    |

| Table 3: Array Addressing for Logical Unit (LUN) for B47R in SLC mode                                       | 27    |

| Table 4: NV-DDR3 Interface Mode Selection                                                                   | 29    |

| Table 5: On-die Termination DC Electrical Characteristics without ZQ Calibration                            | 32    |

| Table 6: On-die Termination DC Electrical Characteristics with ZQ Calibration                               |       |

| Table 7: R <sub>TT(EFF)</sub> Impedance Values with ZQ Calibration                                          | 32    |

| Table 8: LUN state for Matrix Termination                                                                   | 34    |

| Table 9: Volume Appointment for Matrix Termination Example                                                  |       |

| Table 10: Non-Target ODT for Data Output, Target ODT for Data Input Settings Configuration Example          | 37    |

| Table 11: Parallel Non-Target ODT Settings Configuration Example                                            | 38    |

| Table 12: Data Input Sequence Interruption and Resume Requirements if Data Input Sequence is Interrupted by | эу а  |

| CE# HIGH Pulse > 1 µs Duration                                                                              | 41    |

| Table 13: Data Output Sequence Interruption and Resume Requirements if Data Output Sequence is Interrupted  | d by  |

| a CE# HIGH Pulse >1µs Duration                                                                              |       |

| Table 14: Feature Address 20h: DCC Training and Write DQ Training (Tx Side)                                 |       |

| Table 15: Read Training User Defined Pattern Example Table (Inverse Setting and Bytes 0–15)                 |       |

| Table 16: Read Training User Defined Pattern Example Table (Bytes 16–31)                                    | 64    |

| Table 17: Command Set                                                                                       |       |

| Table 18: Read Assist Features                                                                              |       |

| Table 19: Read ID Parameters for Address 00h                                                                |       |

| Table 20: Read ID Parameters for Address 20h                                                                |       |

| Table 21: Read ID Parameters for Address 40h                                                                |       |

| Table 22: ONFI Parameter Page Data Structure                                                                | 80    |

| Table 23: JEDEC Parameter Page Definition                                                                   |       |

| Table 24: Feature Address Definitions                                                                       |       |

| Table 25: GET/SET FEATURES by LUN Operation LUN address cycle decoding                                      |       |

| Table 26: Feature Address 01h: Timing Mode                                                                  |       |

| Table 27: Feature Address 02h: NV-DDR3 configuration                                                        |       |

| Table 28: Feature Addresses 10h: Programmable Output Drive Strength                                         |       |

| Table 29: Feature Address 30h: V <sub>PP</sub>                                                              |       |

| Table 30: Feature Address 58h: Volume configuration                                                         |       |

| Table 31: Feature Addresses 81h: Programmable R/B# Pull-Down Strength                                       |       |

| Table 32: Feature Address 83h: Internal/External ZQ Calibration Switching                                   |       |

| Table 33: Feature Address 84h: Clear Extended Status Register                                               |       |

| Table 34: Feature Address 86h: Read Offset Values Reset                                                     |       |

| Table 35: Feature Address 87h: Sleep Lite                                                                   |       |

| Table 36: LUN state for Matrix Termination with Sleep Lite Feature                                          |       |

| Table 37: Feature Addresses 90h: Array Operation Mode                                                       |       |

| Table 38: Feature Address 96h: Auto Read Calibration and Address Cycle Read Retry                           |       |

| Table 39: Feature Address A0h-ABh Settings                                                                  |       |

| Table 40: Feature Addresses B1h-B4h, E1h-E3h: SBSBR                                                         |       |

| Table 41: Feature Address DAh: Thermal Alert                                                                |       |

| Table 42: NAND Operations and Thermal Alert                                                                 |       |

| Table 43: Feature Address E7h: Temperature Sensor Readout                                                   |       |

| Table 44: Temperature Sensor Readout Parameter                                                              |       |

| Table 45: Volume Address                                                                                    |       |

| Table 46: ODT Configuration Matrix                                                                          |       |

| Table 47: Example of ODT Matrix Configuration for LUNs in Non-Mirrored and Mirrored Modes                   |       |

| Table 48: LUN Address Cycle Decoding                                                                        |       |

| Table 49: I/O Drive Strength Settings                                                                       | . 125 |

| Table 50: Status Register (SR) Definition                                                              |     |

|--------------------------------------------------------------------------------------------------------|-----|

| Table 51: Extended Status Register (ESR) Definition                                                    |     |

| Table 52: Program Suspend SR[3] and Erase Suspend SR[2] Behavior                                       |     |

| Table 53: Status Command Use After Initial Operation                                                   |     |

| Table 54: R1 Address Cycle Decoding for 71h Operation                                                  |     |

| Table 55: Read Operations with <sup>t</sup> R Reduction Functionality                                  | 138 |

| Table 56: Only Valid Commands when die (LUN) is Ready (RDY = 1, ARDY = 0) for READ PAGE (00h-30h), RE  |     |

| PAGE CACHE-series (31h, 00h-31h, 3Fh), and READ PAGE MULTI-PLANE (00h-32h)                             |     |

| Table 57: Offset Cycle Encoding.                                                                       | 147 |

| Table 58: Multi-Plane Read Operation Applied Prefix Offset                                             |     |

| Table 59: Valid Commands and Feature Addresses.                                                        |     |

| Table 60: List of Valid NAND Array Operations Interaction with IWL                                     |     |

| Table 61: Read Feature Compatibility Table                                                             |     |

| Table 62: FEATURE ADDRESS A0h-ABh Settings                                                             |     |

| Table 63: Definitions for Feature Addresses A0h-ABh                                                    |     |

| Table 64: FEATORE ADDRESS A011-ABII: P1/P2/P3 Sub-leature values and Corresponding voltage Offset val  | ues |

| Table 65: Behavioral Summary for Auto Read Calibration Feature                                         | 165 |

| Table 66: Definitions for Feature Addresses B1h-B4h, E1h-E3h                                           |     |

| Table 67: SBSBR Subfeature Parameter Setting for Feature Addresses B1h-B4h, E1h-E3h                    |     |

| Table 68: Valid Operations with SLC MODE LUN ENABLE (3Bh)                                              |     |

| Table 69: NAND Mode for SLC Entry with Auto Exit Option                                                |     |

| Table 70: PROGRAM SUSPEND (84h) Status Details                                                         |     |

| Table 71: Feature Address 7Fh: Manual Dynamic Word Line Start Voltage                                  |     |

| Table 72: ERASE SUSPEND (61h) Status Details                                                           |     |

| Table 73: ERASE SUSPEND (61h) Behavior for ERASE Operations                                            |     |

| Table 74: NESTED SUSPEND Status Details                                                                |     |

| Table 75: Restrictions During Suspend State                                                            |     |

| Table 76: OTP Area Details                                                                             |     |

| Table 77: Error Management Details                                                                     |     |

| Table 78: Shared Pages                                                                                 |     |

| Table 79: Output Drive Strength Conditions (V <sub>CCQ</sub> = 1.14–1.26V)                             | 226 |

| Table 80: Output Drive Strength Impedance Values Without ZQ Calibration ( $V_{CCO} = 1.14-1.26V$ )     | 226 |

| Table 81: Output Drive Strength Impedance Values With ZQ Calibration ( $V_{CCQ} = 1.14-1.26V$ )        | 227 |

| Table 82: Output Drive Sensitivity With ZQ Calibration                                                 | 228 |

| Table 83: Output Driver Voltage and Temperature Sensitivity With ZQ Calibration                        |     |

| Table 84: Pull-Up and Pull-Down Output Impedance Mismatch Without ZQ Calibration for NV-DDR3           |     |

| Table 85: Pull-Up and Pull-Down Output Impedance Mismatch With ZQ Calibration for NV-DDR3              |     |

| Table 86: NV-DDR3 Overshoot/Undershoot Parameters For Timing Modes 0–12                                |     |

| Table 87: NV-DDR3 Overshoot/Undershoot Parameters For Timing Modes 13–15                               |     |

| Table 88: Test Conditions for Input Slew Rate                                                          |     |

| Table 89: Maximum and Minimum Input Slew Rate                                                          |     |

| Table 90: Input Slew Rate Derating for NV-DDR3 Single-Ended ( $V_{CCQ} = 1.14-1.26V$ ) - ps Units      | 233 |

| Table 91: Input Slew Rate Derating for NV-DDR3 Differential ( $V_{CCQ} = 1.14-1.26V$ ) - ps Units      |     |

| Table 92: Test Conditions for Output Slew Rate                                                         |     |

| Table 93: Output Slew Rate Matching Ratio for NV-DDR3 Without ZQ Calibration                           |     |

| Table 94: Output Slew Rate for Single-Ended NV-DDR3 ( $V_{CCQ} = 1.14-1.26$ V) With ZQ Calibration     | 238 |

| Table 95: Output Slew Rate for Differential NV-DDR3 (V <sub>CCQ</sub> = 1.14-1.26) With ZQ Calibration |     |

| Table 96: Output Slew Rate Matching Ratio for NV-DDR3 With ZQ Calibration                              |     |

| Table 97: Power Cycle Requirements                                                                     |     |

| Table 99: Recommended Operating Conditions                                                             |     |

| Table 100: Valid Blocks per LUN                                                                        |     |

| table 100. valia biocks per norv                                                                       | 41  |

| Table 101: Input Capacitance: 132-Ball BGA Package                                                                 | 242 |

|--------------------------------------------------------------------------------------------------------------------|-----|

| Table 102: Package Electrical Specifications                                                                       |     |

| Table 103: LUN Pad Specifications                                                                                  |     |

| Table 104: Test Conditions                                                                                         |     |

| Table 105: DC Characteristics and Operating Conditions (NV-DDR3 Interface) 1.2V V <sub>CCO</sub>                   | 245 |

| Table 106: DC Characteristics and Operating Conditions (NV-DDR3 Interface) 1.2V V <sub>CCQ</sub> for Die (LUN) cou |     |

| CE#                                                                                                                |     |

| Table 107: NV-DDR3 DC Characteristics and Operating Conditions for Single-Ended Signals (1.2V V <sub>CCO</sub> )   | 248 |

| Table 108: NV-DDR3 DC Characteristics and Operating Conditions for Differential Signals (1.2V V <sub>CCO</sub> )   | 249 |

| Table 109: Single-Ended Levels for RE_t, RE_c, DQS_t, DQS_c for NV-DDR3 (1.2V V <sub>CCQ</sub> )                   | 250 |

| Table 110: Differential AC Input/Ouput Parameters                                                                  |     |

| Table 111: AC Characteristics: NV-DDR3 Command, Address, and Data for Modes 0-4                                    | 251 |

| Table 112: AC Characteristics: NV-DDR3 Command, Address, and Data for Timing Modes 5–7                             | 256 |

| Table 113: AC Characteristics: NV-DDR3 Command, Address, and Data for Timing Modes 8–10                            | 261 |

| Table 114: AC Characteristics: NV-DDR3 Command, Address, and Data for Timing Modes 11–15                           | 265 |

| Table 115: TLC Array Characteristics                                                                               | 273 |

| Table 116: SLC Array Characteristics                                                                               | 275 |

|                                                                                                                    |     |

### TLC 512Gb-8Tb NAND Important Notes and Warnings

## **Important Notes and Warnings**

Micron Technology, Inc. ("Micron") reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions. This document supersedes and replaces all information supplied prior to the publication hereof. You may not rely on any information set forth in this document if you obtain the product described herein from any unauthorized distributor or other source not authorized by Micron.

Automotive Applications. Products are not designed or intended for use in automotive applications unless specifically designated by Micron as automotive-grade by their respective data sheets. Distributor and customer/distributor shall assume the sole risk and liability for and shall indemnify and hold Micron harmless against all claims, costs, damages, and expenses and reasonable attorneys' fees arising out of, directly or indirectly, any claim of product liability, personal injury, death, or property damage resulting directly or indirectly from any use of non-automotive-grade products in automotive applications. Customer/distributor shall ensure that the terms and conditions of sale between customer/distributor and any customer of distributor/customer (1) state that Micron products are not designed or intended for use in automotive applications unless specifically designated by Micron as automotive-grade by their respective data sheets and (2) require such customer of distributor/customer to indemnify and hold Micron harmless against all claims, costs, damages, and expenses and reasonable attorneys' fees arising out of, directly or indirectly, any claim of product liability, personal injury, death, or property damage resulting from any use of non-automotive-grade products in automotive applications.

Critical Applications. Products are not authorized for use in applications in which failure of the Micron component could result, directly or indirectly in death, personal injury, or severe property or environmental damage ("Critical Applications"). Customer must protect against death, personal injury, and severe property and environmental damage by incorporating safety design measures into customer's applications to ensure that failure of the Micron component will not result in such harms. Should customer or distributor purchase, use, or sell any Micron component for any critical application, customer and distributor shall indemnify and hold harmless Micron and its subsidiaries, subcontractors, and affiliates and the directors, officers, and employees of each against all claims, costs, damages, and expenses and reasonable attorneys' fees arising out of, directly or indirectly, any claim of product liability, personal injury, or death arising in any way out of such critical application, whether or not Micron or its subsidiaries, subcontractors, or affiliates were negligent in the design, manufacture, or warning of the Micron product.

Customer Responsibility. Customers are responsible for the design, manufacture, and operation of their systems, applications, and products using Micron products. ALL SEMICONDUCTOR PRODUCTS HAVE INHERENT FAILURE RATES AND LIMITED USEFUL LIVES. IT IS THE CUSTOMER'S SOLE RESPONSIBILITY TO DETERMINE WHETHER THE MICRON PRODUCT IS SUITABLE AND FIT FOR THE CUSTOMER'S SYSTEM, APPLICATION, OR PRODUCT. Customers must ensure that adequate design, manufacturing, and operating safeguards are included in customer's applications and products to eliminate the risk that personal injury, death, or severe property or environmental damages will result from failure of any semiconductor component.

Limited Warranty. In no event shall Micron be liable for any indirect, incidental, punitive, special or consequential damages (including without limitation lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort, warranty, breach of contract or other legal theory, unless explicitly stated in a written agreement executed by Micron's duly authorized representative.

### **TLC 512Gb-8Tb NAND General Description**

# **General Description**

Micron NAND devices use a highly multiplexed 8-bit bus (DOx) to transfer commands, address, and data. There are five control signals used to implement in the data interface: CE#, CLE, ALE, WE#, and RE#. Additional signals control hardware write protection (WP#) and monitor device status (R/B#).

This Micron NAND Flash device includes a NV-DDR3 data interface for high-performance I/O operations. Data transfers include a bidirectional data strobe (DOS).

This hardware interface creates a low pin-count device with a standard pinout that remains the same from one density to another, enabling future upgrades to higher densities with no board redesign.

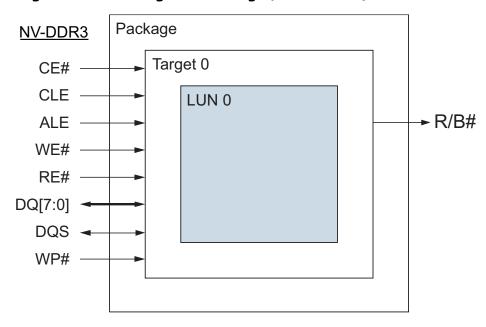

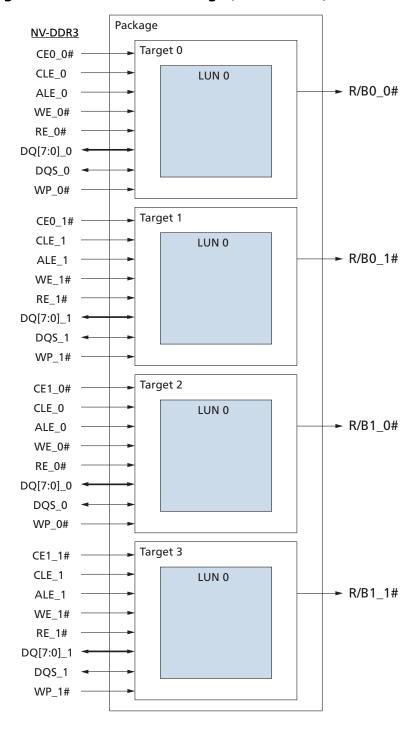

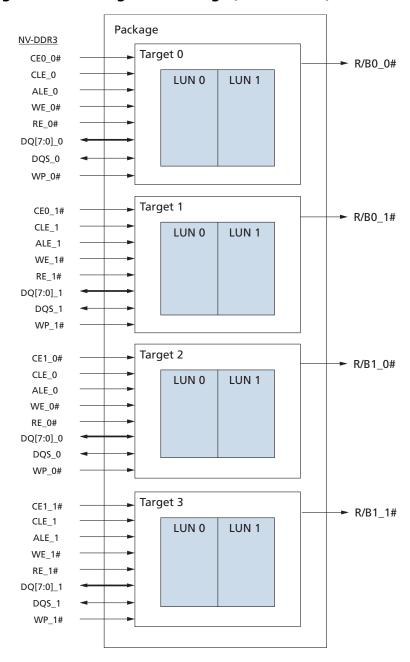

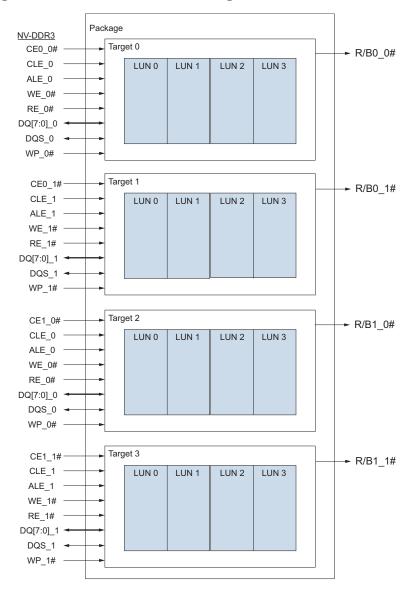

A target is the unit of memory accessed by a chip enable signal. A target contains one or more NAND Flash die, A NAND Flash die is the minimum unit that can independently execute commands and report status. A NAND Flash die, in the ONFI specification, is referred to as a logical unit (LUN). For further details, see Device and Array Organization.

# **NV-DDR3 Signal Descriptions**

#### **Table 1: NV-DDR3 Signal Definitions**

| NV-DDR3 Signal <sup>1</sup> | Туре   | Description <sup>2</sup>                                                                                                                                                                                                                                                                                                              |  |  |  |

|-----------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| ALE                         | Input  | Address latch enable:Loads an address from DQx into the address register.                                                                                                                                                                                                                                                             |  |  |  |

| CE#                         | Input  | hip enable: Enables or disables one or more die (LUNs) in a target.                                                                                                                                                                                                                                                                   |  |  |  |

| CLE                         | Input  | Command latch enable: Loads a command from DQx into the command register.                                                                                                                                                                                                                                                             |  |  |  |

| DQx                         | I/O    | <b>Data inputs/outputs:</b> The bidirectional I/Os transfer address, data, and command information.                                                                                                                                                                                                                                   |  |  |  |

| DQS, DQS_t                  | I/O    | Data strobe: Provides a synchronous reference for data input and output.                                                                                                                                                                                                                                                              |  |  |  |

| DQS_c                       | I/O    | <b>Data strobe complement:</b> Provides a complementary signal to the data strobe signal optionally used for reference for data input and output.                                                                                                                                                                                     |  |  |  |

| RE#, RE_t                   | Input  | <b>Read enable:</b> RE# transfers serial data from the NAND Flash to the host system.                                                                                                                                                                                                                                                 |  |  |  |

| RE_c                        | Input  | <b>Read enable complement:</b> Provides a complementary signal to the read enable signal optionally used for reference for data output.                                                                                                                                                                                               |  |  |  |

| WE#                         | Input  | Write enable: WE# transfers commands, addresses.                                                                                                                                                                                                                                                                                      |  |  |  |

| WP#                         | Input  | Write protect: Enables or disables array PROGRAM and ERASE operations.                                                                                                                                                                                                                                                                |  |  |  |

| R/B#                        | Output | <b>Ready/busy:</b> An open-drain, active-low output that requires an external pull-up resistor. This signal indicates target array activity.                                                                                                                                                                                          |  |  |  |

| V <sub>CC</sub>             | Supply | V <sub>CC</sub> : Core power supply                                                                                                                                                                                                                                                                                                   |  |  |  |

| V <sub>CCQ</sub>            | Supply | V <sub>CCQ</sub> : I/O power supply                                                                                                                                                                                                                                                                                                   |  |  |  |

| V <sub>PP</sub>             | Supply | $V_{PP}$ : The $V_{PP}$ signal is an optional external high voltage power supply to the device. This high voltage power supply may be used to enhance operations (for example, improved power efficiency). If $V_{PP}$ will not be utilized by a host system, that $V_{PP}$ signal location is then defined as a DNU signal location. |  |  |  |

| V <sub>SS</sub>             | Supply | V <sub>ss</sub> : Core ground connection                                                                                                                                                                                                                                                                                              |  |  |  |

| V <sub>SSQ</sub>            | Supply | V <sub>ssQ</sub> : I/O ground connection                                                                                                                                                                                                                                                                                              |  |  |  |

| $V_{REFQ}$                  | Supply | V <sub>REFQ</sub> : Reference voltage                                                                                                                                                                                                                                                                                                 |  |  |  |

## **TLC 512Gb-8Tb NAND NV-DDR3 Signal Descriptions**

## **Table 1: NV-DDR3 Signal Definitions (Continued)**

| NV-DDR3 Signal <sup>1</sup> | Туре | Description <sup>2</sup>                                                                                                                            |

|-----------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| ZQ                          | -    | <b>Reference pin for ZQ calibration</b> : This is used on ZQ calibration. The ZQ signal shall be connected to Vss through R <sub>ZQ</sub> resistor. |

| NC                          | _    | <b>No connect:</b> NCs are not internally connected. They can be driven or left unconnected.                                                        |

| DNU                         | _    | Do not use: DNUs must be left unconnected.                                                                                                          |

| RFU                         | _    | Reserved for future use: RFUs must be left unconnected.                                                                                             |

Notes: 1. See Device and Array Organization and Signal Assignment sections for detailed signal connections.

2. See Bus Operation – NV-DDR3 Interface for detailed signal descriptions.

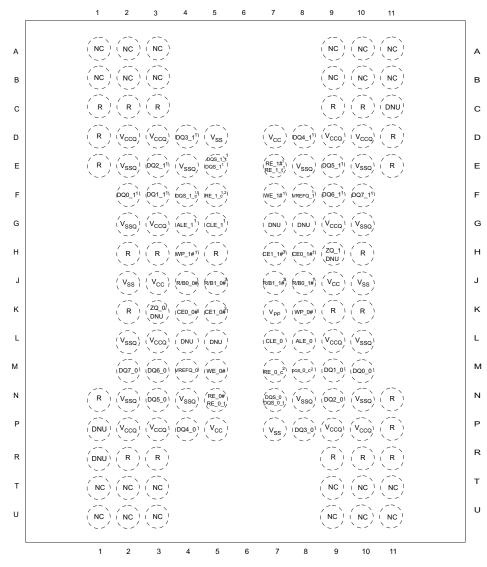

# TLC 512Gb-8Tb NAND Signal Assignments

# **Signal Assignments**

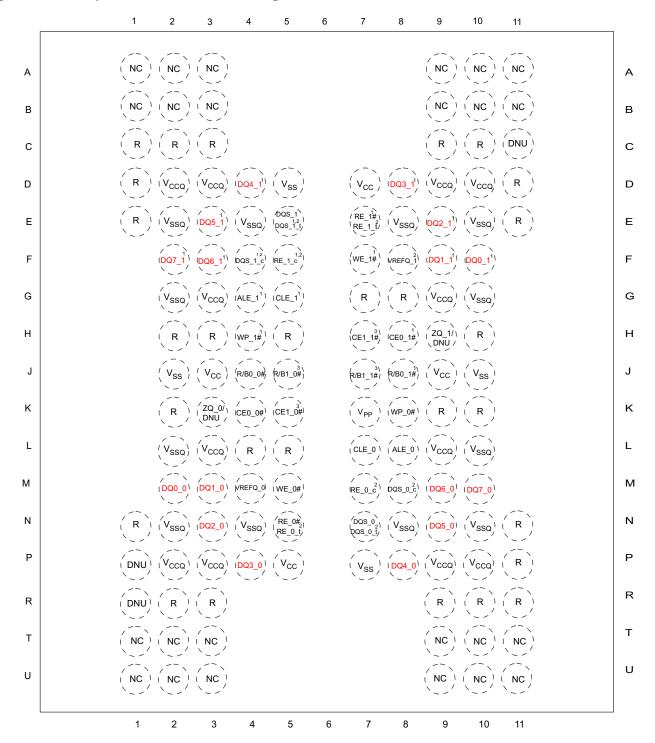

Figure 3: 132-ball BGA (Ball-Down, Top View)

- Notes: 1. These signals are available on dual, quad, octal or higher die stacked die packages. They are NC for other configurations.

- 2. These signals are available when differential signaling is enabled.

- 3. These signals are available on quad die four CE#, octal die, or 16 die stacked packages. They are NC for other configurations.

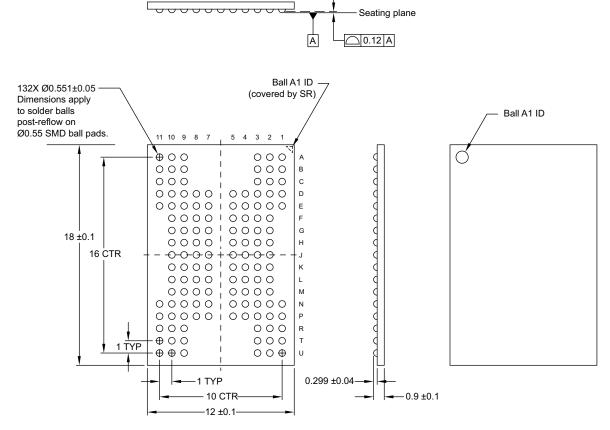

#### **TLC 512Gb-8Tb NAND Package Dimensions**

# **Package Dimensions**

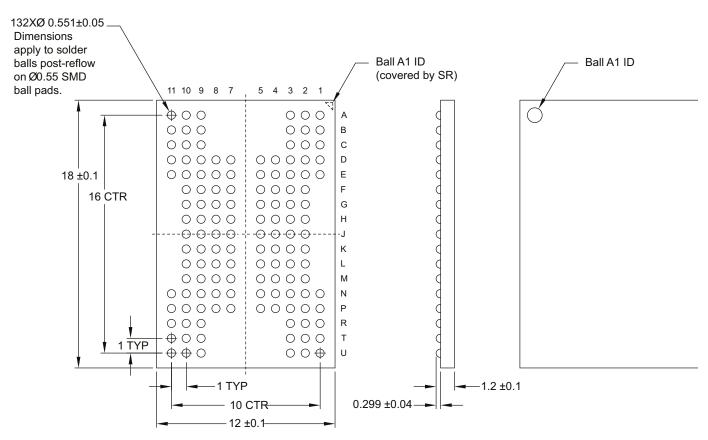

#### Figure 4: 132-Ball VBGA - 12mm x 18mm x 1.0 (Package Code: J4)

- Notes: 1. All dimensions are in millimeters.

- 2. Solder ball material: SACQ (92.45% Sn, 4.0% Ag, 3.0% Bi, 0.5% Cu, 0.05% Ni).

### **TLC 512Gb-8Tb NAND Package Dimensions**

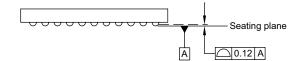

Figure 5: 132-Ball LBGA - 12mm x 18mm x 1.3 (Package Code: M4)

18

Notes: 1. All dimensions are in millimeters.

2. Solder ball material: SACQ (92.45% Sn, 4.0% Ag, 3.0% Bi, 0.5% Cu, 0.05% Ni).

### **TLC 512Gb-8Tb NAND Package Dimensions**

Figure 6: 132-Ball LBGA - 12mm x 18mm x 1.5 (Package Code: M5)

- Notes: 1. All dimensions are in millimeters.

- 2. Solder ball material: SACQ (92.45% Sn, 4.0% Ag, 3.0% Bi, 0.5% Cu, 0.05% Ni).

#### **TLC 512Gb-8Tb NAND Architecture**

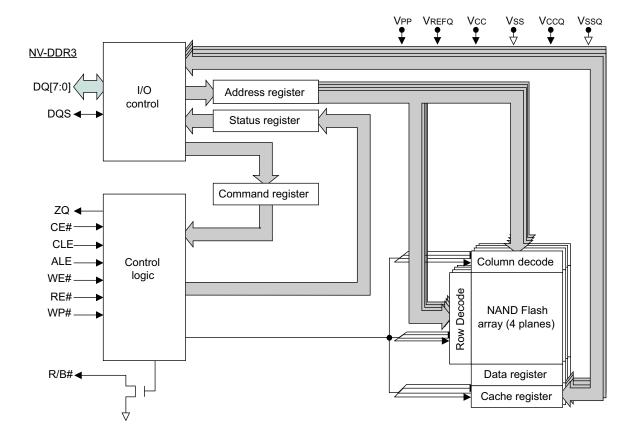

#### Architecture

These devices use NAND Flash electrical and command interfaces. Data, commands, and addresses are multiplexed onto the same pins and received by I/O control circuits. The commands received at the I/O control circuits are latched by a command register and are transferred to control logic circuits for generating internal signals to control device operations. The addresses are latched by an address register and sent to a row decoder to select a row address, or to a column decoder to select a column address.

Data is transferred to or from the NAND Flash memory array, byte by byte, through a data register and a cache register.

The NAND Flash memory array is programmed and read using page-based operations and is erased using block-based operations. During normal page operations, the data and cache registers act as a single register. During cache operations, the data and cache registers operate independently to increase data throughput.

The status register reports the status of die (LUN) operations.

Figure 7: NAND Flash Die (LUN) Functional Block Diagram

## **TLC 512Gb-8Tb NAND Device and Array Organization**

# **Device and Array Organization**

Figure 8: Device Organization for Single-Die Package (132-ball BGA)

Figure 9: Device Organization for Two-Die Package (132-ball BGA)

# TLC 512Gb-8Tb NAND Device and Array Organization

Figure 10: Device Organization for Four-Die Package (132-ball BGA)

## **TLC 512Gb-8Tb NAND Device and Array Organization**

Figure 11: Device Organization for Eight-Die Package (132-ball BGA)

## **TLC 512Gb-8Tb NAND Device and Array Organization**

Figure 12: Device Organization for Sixteen-Die Package (132-ball BGA)

# TLC 512Gb-8Tb NAND Device and Array Organization

Figure 13: Array Organization per Logical Unit (LUN) for B47R in TLC mode

Table 2: Array Addressing for Logical Unit (LUN) for B47R in TLC mode

| Cycle  | DQ7  | DQ6               | DQ5               | DQ4               | DQ3               | DQ2  | DQ1                | DQ0                |

|--------|------|-------------------|-------------------|-------------------|-------------------|------|--------------------|--------------------|

| First  | CA7  | CA6               | CA5               | CA4               | CA3               | CA2  | CA1                | CA0 <sup>2</sup>   |

| Second | LOW  | CA14 <sup>3</sup> | CA13              | CA12              | CA11              | CA10 | CA9                | CA8                |

| Third  | PA7  | PA6               | PA5               | PA4               | PA3               | PA2  | PA1                | PA0                |

| Fourth | BA15 | BA14              | PS13 <sup>5</sup> | PS12 <sup>5</sup> | PA11 <sup>4</sup> | PA10 | PA9                | PA8                |

| Fifth  | BA23 | BA22              | BA21              | BA20              | BA19              | BA18 | BA17               | BA16               |

| Sixth  | LOW  | LOW               | LOW               | LOW               | LOW               | LOW  | LA1 <sup>6,7</sup> | LA0 <sup>6,7</sup> |

- Notes: 1. CAx = column address, PAx = page address, PSx = plane select, BAx = block address, LAx = LUN address; the page address, plane select, block address, and LUN address are collectively called the row address. Consequently, the first and second cycles containing the column addresses are known as C1 and C2, and the third, fourth, fifth, and sixth cycles containing the row addresses cycles are known as R1, R2, R3, and R4 respectively.

- 2. For NV-DDR3 interface, CA0 is forced to 0 internally; one data cycle always returns one even byte and one odd byte.

- 3. CA [14:0] address column addresses 0 through 18,351 (16,384 + 1968) (47AFh), therefore column addresses 18,352 (47B0h) through 32,767 (7FFFh) are invalid, out of bounds, do not exist in the device, and cannot be addressed.

- 4. PA [11:0] address page addresses 0 through 2111 (83Fh), therefore page addresses 2112 (840h) through 4095 (FFFh) are invalid, out of bounds, and do not exist in the device. It is not allowed to issue any PROGRAM, READ, ERASE, or any other array operation on out of bounds pages.

- 5. PS[13:12] are the plane-select bits:

Plane 0: PS[13:12] = 00b

Plane 1: PS[13:12] = 01b

Plane 2: PS[13:12] = 10b

Plane 3: PS[13:12] = 11b

6. LA0, LA1 are the LUN-select bits. They are present only when two or more LUNs are shared on the target; otherwise, they should be held LOW.

LUN 0: LA0 = 0, LA1 = 0

LUN 1: LA0 = 1, LA1 = 0

LUN 2: LA0 = 0, LA1 = 1

LUN 3: LA0 = 1, LA1 = 1

The sixth address cycle is required for all LUN per Target (CE#) configurations (i.e. 1, 2, and 4 LUNs per CE#) regardless if a LUN-select bit is present in the sixth address cycle. If there is no LUN-select bit present in the sixth address cycle then the sixth address cycles is required to be 00h.

7. For single LUN Targets block addresses 2224 through 4095 are invalid, out of bounds, and do not exist in the device. For two LUN Targets block addresses 2224 through 4095 and 6320 through 8191 are invalid, out of bounds, and

### **TLC 512Gb-8Tb NAND Device and Array Organization**

do not exist in the device.

For four LUN Targets block addresses 2224 through 4095, 6320 through 8191, 10,416 through 12,287, and 14,512 through 16,383 are invalid, out of bounds, and do not exist in the device.

It is not allowed to issue any PROGRAM, READ, ERASE, or any other array operation on out of bounds blocks.

# TLC 512Gb-8Tb NAND Device and Array Organization

Figure 14: Array Organization per Logical Unit (LUN) for B47R in SLC mode

Table 3: Array Addressing for Logical Unit (LUN) for B47R in SLC mode

| Cycle  | DQ7  | DQ6               | DQ5               | DQ4               | DQ3  | DQ2  | DQ1                | DQ0                |

|--------|------|-------------------|-------------------|-------------------|------|------|--------------------|--------------------|

| First  | CA7  | CA6               | CA5               | CA4               | CA3  | CA2  | CA1                | CA0 <sup>2</sup>   |

| Second | LOW  | CA14 <sup>3</sup> | CA13              | CA12              | CA11 | CA10 | CA9                | CA8                |

| Third  | PA7  | PA6               | PA5               | PA4               | PA3  | PA2  | PA1                | PA0                |

| Fourth | BA15 | BA14              | PS13 <sup>5</sup> | PS12 <sup>5</sup> | LOW  | LOW  | PA9 <sup>4</sup>   | PA8                |

| Fifth  | BA23 | BA22              | BA21              | BA20              | BA19 | BA18 | BA17               | BA16               |

| Sixth  | LOW  | LOW               | LOW               | LOW               | LOW  | LOW  | LA1 <sup>6,7</sup> | LA0 <sup>6,7</sup> |

Notes: 1. CAx = column address, PAx = page address, PSx = plane select, BAx = block address, LAx = LUN address; the page address, plane select, block address, and LUN address are collectively called the row address. Consequently, the first and second cycles containing the column addresses are known as C1 and C2, and the third, fourth, fifth, and sixth cycles containing the row addresses cycles are known as R1, R2, R3, and R4 respectively.

- 2. For NV-DDR3 interface, CA0 is forced to 0 internally; one data cycle always returns one even byte and one odd byte.

- 3. CA [14:0] address column addresses 0 through 18,351 (16,384 + 1968) (47AFh), therefore column addresses 18,352 (47B0h) through 32,767 (7FFFh) are invalid, out of bounds, do not exist in the device, and cannot be addressed.

- 4. PA [9:0] address page addresses 0 through 703 (2BFh), therefore page addresses 704 (2C0h) through 1023 (3FFh) are invalid, out of bounds, and do not exist in the device. It is not allowed to issue any PROGRAM, READ, ERASE, or any other array operation on out of bounds pages.

- 5. PS[13:12] are the plane-select bits:

Plane 0: PS[13:12] = 00b

Plane 1: PS[13:12] = 01b

Plane 2: PS[13:12] = 10b

Plane 3: PS[13:12] = 11b

6. LA0, LA1 are the LUN-select bits. They are present only when two or more LUNs are shared on the target; otherwise, they should be held LOW.

LUN 0: LA0 = 0, LA1 = 0

LUN 1: LA0 = 1, LA1 = 0

LUN 2: LA0 = 0, LA1 = 1

LUN 3: LA0 = 1, LA1 = 1

The sixth address cycle is required for all LUN per Target (CE#) configurations (i.e. 1, 2, and 4 LUNs per CE#) regardless if a LUN-select bit is present in the sixth address cycle. If there is no LUN-select bit present in the sixth address cycle then the sixth address cycles is required to be 00h.

### **TLC 512Gb-8Tb NAND Device and Array Organization**

- 7. For single LUN Targets block addresses 2224 through 4095 are invalid, out of bounds, and do not exist in the device. For two LUN Targets block addresses 2224 through 4095 and 6320 through 8191 are invalid, out of bounds, and do not exist in the device.

- For four LUN Targets block addresses 2224 through 4095, 6320 through 8191, 10,416 through 12,287, and 14,512 through 16,383 are invalid, out of bounds, and do not exist in the device.

- It is not allowed to issue any PROGRAM, READ, ERASE, or any other array operation on out of bounds blocks.

## **Bus Operation – NV-DDR3 Interface**

The NV-DDR3 interface is capable of high-speed DDR data transfers and the DQS signal is enabled. DQS is a bidirectional data strobe. During data output, DQS is driven by the NAND Flash device. During data input, DQS is controlled by the host controller while inputting data on DQ[7:0].

Use of differential signaling, external  $V_{REFQ}$ , and ZQ calibration is optional for interface speeds 200 MT/s or slower. Differential signaling and external  $V_{REFQ}$  are optional for NV-DDR3 interface speeds faster than 200 MT/s but required to guarantee specified AC timings. If a host does not use differential signaling and external  $V_{REFQ}$  at speeds faster than 200 MT/s, specified AC timings are not guaranteed. If not using the differential signaling, statements about those signal types can be ignored. ZQ calibration is optional for NV-DDR3 interface speeds faster than 533 MT/s but required to guarantee specified AC timings. If a host does not use ZQ calibration at speeds faster than 533 MT/s, specified AC timings are not guaranteed.

The NV-DDR3 interface bus modes are summarized below:

**Table 4: NV-DDR3 Interface Mode Selection**

| Mode          | CE# | CLE | ALE | RE#<br>(RE_t) | RE_c <sup>8</sup> | DQS<br>(DQS_t) | DQS_c <sup>8</sup> | DQ[7:0] <sup>1</sup> | WE#      | WP#                 | Notes   |